# e<sub>2</sub>V

**AT84AD001-EB Evaluation Kit**

**User Guide**

### e<sub>2</sub>v

#### Table of Contents

| Secti  | ion   | 1    |                                                      |      |

|--------|-------|------|------------------------------------------------------|------|

| Introd | ducti | on.  |                                                      | 1-1  |

|        | 1.1   | Sc   | ope                                                  | 1-1  |

|        | 1.2   | De   | scription                                            | 1-1  |

| Secti  | ion z | 2    |                                                      |      |

| Hard   | ware  | e De | escription                                           | 2-1  |

| 2      | 2.1   | Во   | ard Structure                                        | 2-1  |

| 2      | 2.2   | An   | alog and Clock Inputs/ Digital Outputs               | 2-2  |

|        | 2.3   | Po   | wer Supplies                                         | 2-2  |

| Secti  | ion : | 3    |                                                      |      |

| Opera  | atin  | g Cl | haracteristics                                       |      |

| and F  | roc   | edu  | ıres                                                 | 3-1  |

|        | 3.1   |      | roduction                                            |      |

|        | 3.2   |      | perating Procedure                                   |      |

| (      | 3.3   |      | ectrical Characteristics                             |      |

|        | 3.3   |      | Timing Diagrams                                      |      |

|        | 3.3   | 3.2  | Digital Coding                                       | 3-11 |

| ;      | 3.4   | Te   | st and Control Features                              | 3-12 |

|        | 3.4   | .1   | 3-wire Serial Interface Control Settings             | 3-12 |

|        | 3.4   | .2   | 3-wire Serial Interface Address and Data Description | 3-12 |

|        | 3.4   | .3   | 3-wire Serial Interface Timing Description           | 3-16 |

|        | 3.4   | .4   | Calibration Description                              | 3-18 |

|        | 3.4   | .5   | Gain and Offset Compensation Functions               |      |

|        | 3.4   | .6   | Built-In Test                                        |      |

|        | 3.4   | .7   | Decimation Mode                                      | 3-20 |

| Secti  | ion i | 4    |                                                      |      |

|        |       |      | ols                                                  | 4-1  |

|        | 4.1   |      | verview                                              |      |

| 4      | 4.2   | Со   | nfiguration                                          | 4-1  |

| 4      | 4.3   | Ge   | etting Started                                       | 4-1  |

| 4      | 4.4   | Ins  | stallation Software                                  | 4-8  |

| 4      | 4.5   | Ор   | perating Modes                                       | 4-9  |

|        | 4.5   | 5.1  | Overview                                             | 4-9  |

|        | 4.5   | 5.2  | Control Mode                                         | 4-10 |

|        | 4.5   | 5.3  | DEMUX Mode                                           | 4-10 |

i

|       | 4.5.4    | Data Ready Type                                       | 4-10    |

|-------|----------|-------------------------------------------------------|---------|

|       | 4.5.5    | Output Mode                                           | 4-11    |

|       | 4.5.6    | Decimation Mode                                       | 4-11    |

|       | 4.5.7    | Standby Mode                                          | 4-11    |

|       | 4.5.8    | Calibration Mode                                      | 4-12    |

|       | 4.5.9    | Analog Input Signal Selection                         | 4-12    |

|       | 4.5.10   | Clock Selection                                       | 4-12    |

|       | 4.5.11   | Gain Adjust                                           | 4-13    |

|       | 4.5.12   | Gain Compensation                                     | 4-13    |

|       | 4.5.13   | Offset Adjust                                         | 4-13    |

|       | 4.5.14   | Internal Setting Adjustment                           | 4-14    |

|       | 4.5.15   | Data Ready Delay Adjust                               | 4-14    |

|       | 4.5.16   | Fine Sampling Delay Adjust                            | 4-14    |

|       | 4.5.17   | Test Mode                                             | 4-14    |

|       | 4.5.18   | Built-In Test                                         | 4-15    |

| Secti | on 5     |                                                       |         |

|       |          | nformation                                            | 5-1     |

| 5     | 5.1 Ana  | alog Input                                            | 5-1     |

|       |          | ck Input                                              |         |

|       |          | ta Output Termination                                 |         |

| ŧ     |          | ntrol Function Settings                               |         |

|       | 5.4.1    | ADC Gain Adjust                                       |         |

|       | 5.4.2    | ADC Offset Adjust                                     |         |

|       | 5.4.3    | ADC Gain Compensation                                 |         |

|       | 5.4.4    | ADC ISA                                               |         |

|       | 5.4.5    | Data Ready Delay Adjust                               |         |

|       | 5.4.6    | Fine Sampling Delay Adjust                            | 5-6     |

|       | 5.4.7    | Die Junction Temperature Monitoring                   |         |

|       | 5.4.8    | Asynchronous Data Ready Reset I and Q                 | 5-7<br> |

| Secti | on 6     |                                                       |         |

| Order | •        | ormation                                              |         |

| 6     | 6.1 Ord  | dering Information                                    | 6-1     |

| Secti | on 7     |                                                       |         |

| Appeı | ndices . |                                                       | 7-1     |

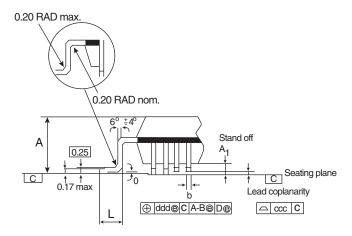

| 7     |          | Pulse Transformer                                     |         |

| 7     |          | ) kHz/1.5 GHz TP101: M/A-COM7-1 ard Layout Schematics | 7-2     |

| ,     |          | ara =a,, oar oononuunoo                               |         |

### e<sub>2</sub>v

### **Section 1**

### Introduction

#### 1.1 Scope

The AT84AD001-EB Evaluation Kit is designed to facilitate the evaluation and characterization of the AT84AD001B dual 8-bit 1 Gsps ADC.

The AT84AD001-EB Evaluation Kit includes:

- The dual 8-bit 1 Gsps ADC evaluation board.

- A cable for connection to the RS-232 port.

- 8 SMA caps for CLKQ, CLKQN, CLKI, CLKIN, VINQ, VINQB, VINI, VINIB SMAs.

- Software tools necessary for the use of the 3-wire serial digital interface.

This user guide uses the AT84AD001-EB Evaluation Kit as an evaluation and demonstration platform and provides guidelines for its proper use.

This user guide usually refers to the dual 8-bit 1 Gsps ADC datasheet ref. 0817F.

#### 1.2 Description

Thanks to its user-friendly interface, the AT84AD001-EB Evaluation Kit enables testing of all the functions of the AT84AD001B dual 8-bit 1 Gsps ADC:

- Input clock selection

- Analog input switch selection

- Autocalibration function

- Gain and offset control

- Standby mode

- 1:1 or 1:2 demultiplexer function

- Die junction temperature monitoring function

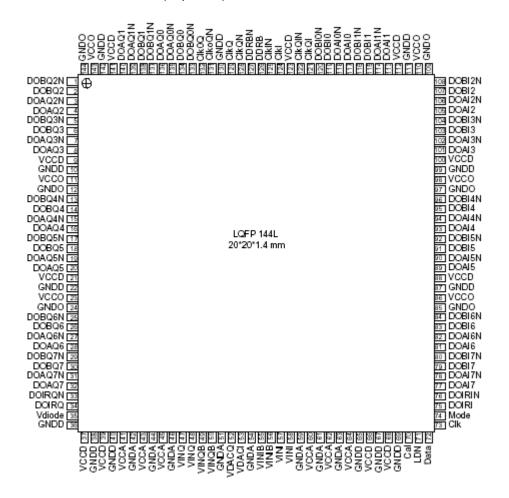

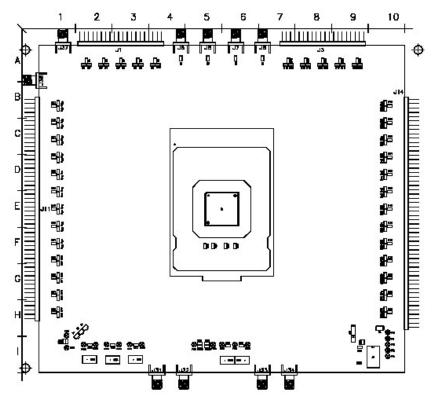

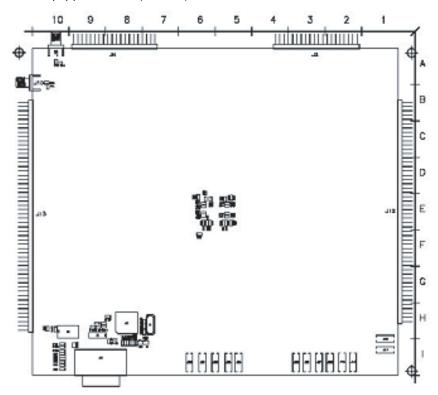

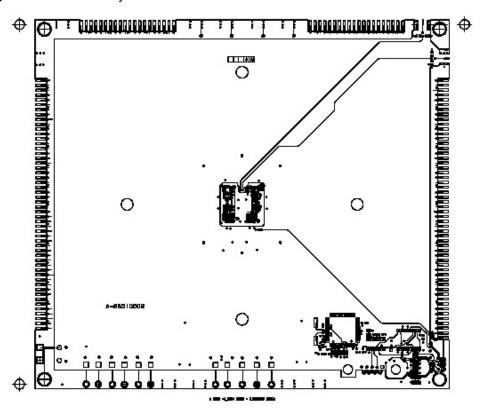

To achieve optimal performance, the AT84AD001-EB Evaluation Board was designed in a 4-metal-layer board with FR4 dielectric layers. The board implements the following devices:

- The AT84AD001B dual 8-bit 1 Gsps ADC device

- SMA connectors for the analog and clock inputs

- 2.54 mm pitch connectors for the digital data and clock inputs (compatible with high frequency acquisition system probes)

- An RS-232 connector for PC interface

- Banana jacks for the power supply accesses

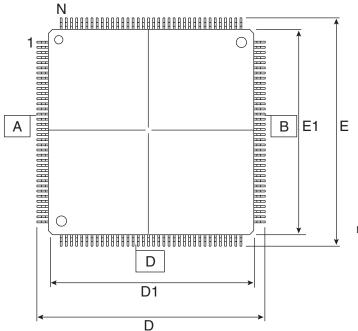

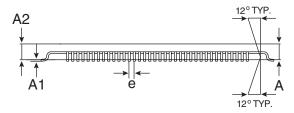

The board is made of four metal layers for signal traces, ground and power supply layers, and three dielectric layers featuring low insertion loss and enhanced thermal characteristics for operation in the high frequency domain. The board dimensions are  $193 \text{ mm} \times 216 \text{ mm}$ .

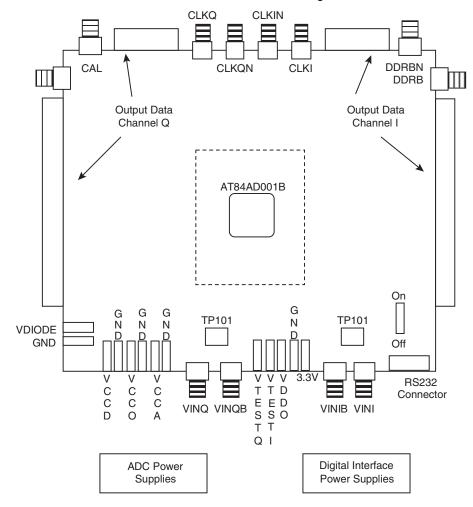

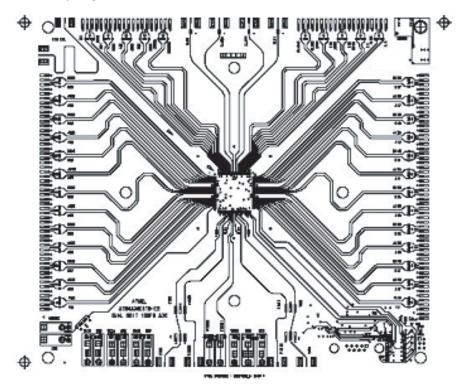

Figure 1-1. AT84AD001-EB Evaluation Board Block Diagram

As shown in Figure 1-1, five different power supplies are required:

- V<sub>CCA</sub> = 3.3V ADC analog power supply

- V<sub>CCD</sub> = 3.3V ADC digital power supply

- $V_{CCO}$  = 2.25V ADC output power supply

- $V_{DDO}$  = 2.25V digital interface power supply (can be connected to  $V_{CCO}$ )

- 3.3V digital interface primary power supply for the microcontroller

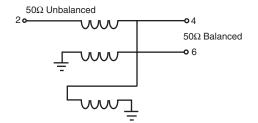

Finally, two RF transformers (TP-101) are provided for the analog inputs ( $V_{INI}$  and  $V_{INQ}$ ). They enable you to operate the ADC in differential mode via single-ended analog inputs.

1-2 AT84AD001-EB - User Guide

### **Section 2**

### **Hardware Description**

#### 2.1 Board Structure

In order to achieve optimum full-speed operation of the AT84AD001B dual 8-bit 1 Gsps ADC, a multi-layer board structure was retained for the Evaluation Board. Four copper layers are used, respectively dedicated to the signal traces, ground planes and power supply planes. Each layer is separated by an FR4 epoxy dielectric layer.

The following table gives a detailed description of the board's structure.

**Table 2-1.** Board Layer Thickness Profile

| Layer                   | Characteristics                                                                                      |

|-------------------------|------------------------------------------------------------------------------------------------------|

| Layer 1<br>Copper layer | Thickness of copper = 35 $\mu m$ Input signals: $50\Omega$ microstrip lines                          |

| Layer 2                 | Thickness of layer = 200 µm                                                                          |

| FR4 dielectric layer    | Dielectric constant = 4.6                                                                            |

| Layer 3                 | Thickness of copper = 35 µm                                                                          |

| Copper layer            | Reference plane (GND)                                                                                |

| Layer 4                 | Thickness of layer = 400 µm                                                                          |

| FR4 dielectric layer    | Dielectric constant = 4.6                                                                            |

| Layer 5                 | Thickness of copper = 35 μm                                                                          |

| Copper layer            | Power Supplies plane                                                                                 |

| Layer 6                 | Thickness of layer = 860 µm                                                                          |

| FR4 dielectric layer    | Dielectric constant = 4.6                                                                            |

| Layer 7<br>Copper layer | Thickness of copper = 35 µm Reference plane (GND) + DDRB, DDRBN reset signals and calibration signal |

The board is 1.6 mm thick.

The input/output signal traces occupy the top metal layer, except for the DRRB and DRRBN Data Ready Asynchronous Reset signals, which are located on the fourth metal layer, together with the second reference plane. The ground planes occupy the second and fourth planes. The third layer is dedicated to the power supplies (both ADC and digital interfaces).

#### 2.2 Analog and Clock Inputs/ Digital Outputs

The board uses  $50\Omega$  impedance microstrip lines for the differential analog and clock inputs, and the differential digital outputs.

The analog and clock inputs are routed on one layer only (top metal layer), without use of through-hole vias.

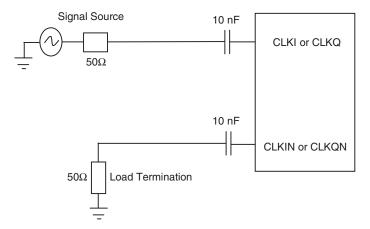

The line lengths are matched to within approximately 1 mm. The clock input lines are AC coupled via 10 nF chip capacitors.

The analog input lines are coupled to ground. In addition, the analog input lines are correctly reverse-terminated by  $50\Omega$  surface mount chip resistors, which are placed very close to the ADC device.

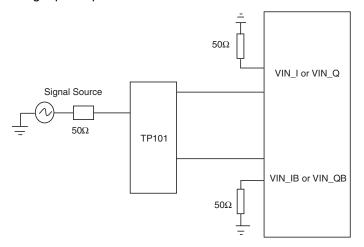

The analog inputs are accessed via SMA connectors in single-ended fashion. The signals are then translated to differential signals by way of two RF transformers (one for each channel). The transformers used are of TP-101 type (see "Appendices" on page 1 for more information).

The output data trace lengths are matched to within approximately 5 mm to minimize the data output skew.

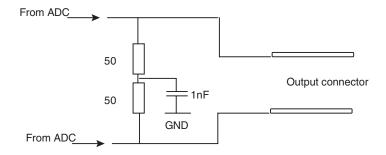

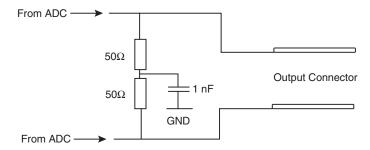

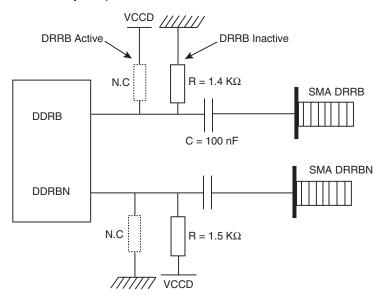

All digital outputs are  $50\Omega$  differentially terminated to ground via a 1 nF chip capacitor, as shown in Figure 2-1.

Figure 2-1. Data Output Differential On-board Termination

The digital output data is accessed via two rows of 2.54 mm pitch connectors, as illustrated in Figure 2-2.

Figure 2-2. Output Data 2.54 mm Pitch Connector

#### 2.3 **Power Supplies**

The fifth metal layer is dedicated to the ADC's power supplies and to the digital interface  $(V_{CCA}, V_{CCD}, V_{CCO}, V_{DDO}, 3.3V)$  for the microcontroller).

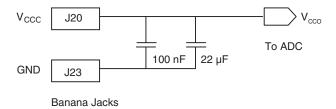

Each incoming power supply is decoupled by 22 µF tantalum chip capacitors in parallel to a 100 pF ceramic chip capacitor, located as close as possible to the power supply accesses (banana jacks).

An example is given for  $V_{CCO}$  in Figure 2-3 on page 3.

2-2 AT84AD001-EB - User Guide

Figure 2-3. Power Supply Decoupling Scheme

Each power supply is bypassed very close to the device by 10 nF in parallel to 100 pF chip capacitors.

Note: These capacitors are superimposed with the 100 pF capacitor mounted first.

Hardware Description

2-4 AT84AD001-EB - User Guide

### **Section 3**

# Operating Characteristics and Procedures

#### 3.1 Introduction

This section describes a typical configuration for analog and clock inputs.

The Evaluation Board is designed to facilitate the evaluation and the characterization of the AT84AD001B dual 8-bit 1Gsps ADC.

The input signals are accessed in single-ended fashion and the RF transformer is used to translate them into differential signals.

Note: For proper operation of the ADC, the analog input signal has to be used in differential mode using an RF transformer.

The clock inputs are accessed in single-ended or differential mode, with a preference for the single-ended configuration as it corresponds to the easiest and quickest setting for evaluating the AT84AD001B dual 8-bit 1Gsps ADC.

The RF sources can be connected directly to the ADC's in-phase clock input.

### 3.2 Operating Procedure

- 1. Connect the ADC's power supplies and ground accesses ( $V_{CCA} = 3.3V$ , GND = 0V,  $V_{CCD} = 3.3V$ ,  $V_{CCO} = 2.25V$ ) through the dedicated banana jacks.  $V_{CCA}$  and  $V_{CCD}$  have separated supply planes.

- 2. Connect the serial interface's power supplies and ground accesses ( $V_{DDO}$  = 2.25V, GND = 0V, 3.3V) through the dedicated banana jacks.  $V_{CCO}$  and  $V_{DDO}$  can be connected together.

- Connect the CLKQ or CLKI clock signals (depending on your ADC configuration).

The inverse phase clock inputs CLKQN and CLKIN must be connected to a  $50\Omega$  load. Use a low-phase noise RF source. The clock input level can be set to -9 dBm and should not exceed 6 dBm into a  $50\Omega$  terminal resistor. The clock frequency can range from 50 MHz to 1 Gsps.

Connect the VINQ or VINI input signals (depending on your ADC configuration).

Use a low-phase noise RF source. Full-scale is 0.250V peak-to-peak around 0V (±125 mV). The analog input frequency can range from 1 MHz to 1.5 GHz.

- 5. Connect the high-speed data acquisition system probes to the output connector. The connector pitch (2.54 mm) is compatible with High-speed Digital Acquisition System probes. The digital data is differentially terminated on-board. However, the output data can be intercepted in either single-ended or differential mode.

- 6. Serial interface: connect your PC's RS-232 connector to the Evaluation Board.

- 7. Serial mode inactive: turn off the switch (green LED off).

All instrumentation and connectors are now connected.

- 8. Switch on the ADC supplies first (start with the  $V_{CCA}$  and  $V_{CCD}$  power supplies).

- 9. Serial interface: switch the V<sub>DDO</sub> power supply on first.

- 10. Turn the RF clock generator on.

- 11. Turn the RF input generator on.

- 12. Serial mode inactive: turn off the switch (green LED off) /RESET Mode.

- 13. Serial mode active: turn on the switch (green LED on).

- 14. Serial interface software:

The ADC has been correctly turned on and the serial interface can now be run. The ADC can then be configured as needed by using the specified software tools (refer to Section 4 for further information).

### 3.3 Electrical Characteristics

Table 3-1. Absolute Maximum Ratings

| Parameter                                                         | Symbol                                                                         | Value                          | Unit |

|-------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------|------|

| Analog positive supply voltage                                    | V <sub>CCA</sub>                                                               | 3.6                            | V    |

| Digital positive supply voltage                                   | V <sub>CCD</sub>                                                               | 3.6                            | V    |

| Output supply voltage                                             | V <sub>cco</sub>                                                               | 3.6                            | V    |

| Maximum difference between $V_{CCA}$ and $V_{CCD}$                | V <sub>CCA</sub> to V <sub>CCD</sub>                                           | ± 0.8                          | V    |

| Minimum V <sub>CCO</sub>                                          | V <sub>cco</sub>                                                               | 1.6                            | V    |

| Serial interface 2.25V                                            | $V_{DDO}$                                                                      | 2.5                            | V    |

| Serial interface 3.3V                                             | 3V3                                                                            | 3.6                            | V    |

| Analog input voltage                                              | V <sub>INI</sub> or V <sub>INIB</sub><br>V <sub>INQ</sub> or V <sub>INQB</sub> | 1/-1                           | V    |

| Digital input voltage                                             | V <sub>D</sub>                                                                 | -0.3 to V <sub>CCD</sub> + 0.3 | V    |

| Clock input voltage                                               | V <sub>CLK</sub> or VC <sub>LKB</sub>                                          | -0.3 to V <sub>CCD</sub> + 0.3 | V    |

| Maximum difference between V <sub>CLK</sub> and V <sub>CLKB</sub> | V <sub>CLK</sub> - V <sub>CLKB</sub>                                           | -2 to 2                        | V    |

| Maximum junction temperature                                      | T <sub>J</sub>                                                                 | 125                            | °C   |

| Storage temperature                                               | T <sub>stg</sub>                                                               | -65 to 150                     | °C   |

| Lead temperature (soldering 10s)                                  | T <sub>leads</sub>                                                             | 300                            | °C   |

Note: Absolute maximum ratings are limiting values (referenced to GND = 0V), to be applied individually, while other parameters are within specified operating conditions. Long exposure to maximum ratings may affect device reliability.

3-2 AT84AD001-EB - User Guide

Table 3-2. Recommended Conditions of Use

| Parameter                                      | Symbol                                                                        | Recommended Value                                                               | Unit |

|------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------|

| Analog supply voltage                          | V <sub>CCA</sub>                                                              | 3.3                                                                             | V    |

| Digital supply voltage                         | V <sub>CCD</sub>                                                              | 3.3                                                                             | V    |

| Output supply voltage                          | V <sub>cco</sub>                                                              | 2.25                                                                            | V    |

| Serial interface 2.25V                         | $V_{DDO}$                                                                     | 2.25                                                                            | V    |

| Serial interface 3.3V                          | 3V3                                                                           | 3.3                                                                             | V    |

| Differential analog input voltage (full-scale) | V <sub>INi</sub> -V <sub>IniB</sub> or<br>V <sub>INQ</sub> -V <sub>INQB</sub> | 500                                                                             | mVpp |

| Differential clock input level                 | Vinclk                                                                        | 600                                                                             | mVpp |

| Internal settling adjustment                   | ISA                                                                           | -50                                                                             | ps   |

| Operating temperature range                    | T <sub>Ambient</sub>                                                          | 0 < T <sub>A</sub> < 70 ("C " grade)<br>-40 < T <sub>A</sub> < 85 (" I " grade) | °C   |

$\rm V_{DDO}$  should not differ from  $\rm V_{CCO}$  by more than ±5%.  $\rm I(V_{DDO})$  and I(3V3) should not exceed 100 mA. Note:

The following conditions apply to the electrical operating characteristics given in Table 3-3.

Unless otherwise specified:

- $V_{CCA} = 3.3V$ ;  $V_{CCD} = 3.3V$ ;  $V_{CCO} = 2.25V$

- $V_{INI}$   $V_{INIB}$  or  $V_{INQ}$   $V_{INQB}$  = 500 mVpp full-scale differential input Digital outputs LVDS (100 $\Omega$ )

- $T_A$  (typical) = 25°C. Full temperature range: 0°C <  $T_A$  < 70°C (commercial grade) or -40°C <  $T_A$  < 85°C (industrial grade)

**Table 3-3.** Electrical Operating Characteristics in Nominal Conditions (Gain Setting 0 dB, One Clock Input, No Standby Mode [Full Power Mode], 1:1 DMUX, Calibration Off)

| Parameter                                      | Symbol           | Min  | Тур  | Max  | Unit |

|------------------------------------------------|------------------|------|------|------|------|

| Resolution                                     |                  |      | 8    |      | Bits |

| Power Requirements                             |                  | I    |      |      |      |

| Positive supply voltage                        |                  |      |      |      |      |

| Analog                                         | $V_{CCA}$        | 3.15 | 3.3  | 3.45 | V    |

| Digital                                        | V <sub>CCD</sub> | 3.15 | 3.3  | 3.45 | V    |

| Output digital (LVDS) and serial interface     | $V_{CCO}$        | 2.0  | 2.25 | 2.5  | V    |

| Supply current (typical conditions)            |                  |      |      |      |      |

| Analog                                         | $I_{CCA}$        |      | 150  | 180  | mA   |

| Digital                                        | I <sub>CCD</sub> |      | 230  | 275  | mA   |

| Output                                         | I <sub>cco</sub> |      | 100  | 120  | mA   |

| F                                              |                  |      |      | 120  | ША   |

| Supply current (1:2 DMUX mode)                 |                  |      |      |      |      |

| Analog                                         | $I_{CCA}$        |      | 150  | 180  | _    |

| Digital                                        | $I_{CCD}$        |      | 260  | 310  | mA   |

| Output                                         | $I_{CCO}$        |      | 175  | 210  | mA   |

| Supply current (2 input clocks, 1:2 DMUX mode) |                  |      |      |      |      |

| Analog                                         | $I_{CCA}$        |      | 150  | 180  |      |

| Digital                                        |                  |      | 290  | 350  | mA   |

| Output                                         | I <sub>CCD</sub> |      | 180  | 215  |      |

| Catput                                         | I <sub>cco</sub> |      | 180  | 215  |      |

| Supply current                                 |                  |      |      |      |      |

| (1 channel only, 1:1 DMUX mode)                |                  |      |      |      | 4    |

| Analog                                         | I <sub>CCA</sub> |      | 80   | 95   | mA   |

| Digital                                        | $I_{CCD}$        |      | 160  | 190  | mA   |

| Output                                         | $I_{cco}$        |      | 55   | 65   | mA   |

| Supply current                                 |                  |      |      |      |      |

| (1 channel only, 1:2 DMUX mode)                |                  |      |      |      |      |

| Analog                                         | I <sub>CCA</sub> |      | 80   | 95   | mA   |

| Digital                                        | I <sub>CCD</sub> |      | 170  | 205  | mA   |

| Output                                         | $I_{CCO}$        |      | 90   | 110  | mA   |

|                                                |                  |      |      |      |      |

| Supply current (full standby mode)             | $I_{CCA}$        |      | 12   | 20   | mA   |

| Analog                                         | I <sub>CCD</sub> |      | 24   | 39   | mA   |

| Digital<br>Output                              | I <sub>cco</sub> |      | 3    | 7    | mA   |

| ( )utput                                       | •000             | I .  |      | •    | IIIA |

3-4

*Table 3-3.* Electrical Operating Characteristics in Nominal Conditions (Gain Setting 0 dB, One Clock Input, No Standby Mode [Full Power Mode], 1:1 DMUX, Calibration Off) (Continued)

| Parameter                                                                                                                                 | Symbol                                     | Min                    | Тур                    | Max                    | Unit     |

|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------------|------------------------|------------------------|----------|

| Nominal dissipation (1 clock, 1:1 DMUX mode, 2 channels)                                                                                  | $P_{D}$                                    |                        | 1.4                    | 1.7                    | W        |

| Nominal dissipation (full standby mode)                                                                                                   | stbpd                                      |                        | 120                    |                        | mW       |

| Analog Inputs                                                                                                                             |                                            | 1                      |                        |                        |          |

| Full-scale differential analog input voltage                                                                                              | V <sub>INi</sub> - V <sub>IniB</sub><br>or | 450                    | 500                    | 550                    | mV<br>mV |

| Analog input capacitance I and Q                                                                                                          | V <sub>INQ</sub> - V <sub>INQB</sub>       |                        |                        | 2                      | pF       |

| Full Power input bandwidth (-3 dB)                                                                                                        | FPBW                                       |                        | 1.5                    |                        | GHz      |

| Gain flatness (-0.5dB)                                                                                                                    | 11 000                                     |                        | 500                    |                        | MHz      |

| Clock Input                                                                                                                               |                                            |                        | 300                    |                        | 1011 12  |

| Logic compatibility for clock inputs and DDRB<br>Reset (pins 124,125,126,127,128,129)                                                     |                                            |                        | PECL/ECL/LVD           | 6                      |          |

| PECL/LVDS clock inputs voltages (V <sub>CLKI/IN</sub> or V <sub>CLKQ/QN</sub> ) Differential logical level                                | V <sub>IL</sub> - V <sub>IH</sub>          |                        | 600                    |                        | mV       |

| Clock input power level                                                                                                                   |                                            | -9                     | 0                      | 6                      | dBm      |

| Clock input capacitance                                                                                                                   |                                            |                        | 2                      |                        | pF       |

| Digital Outputs                                                                                                                           |                                            |                        | 1                      |                        |          |

| Logic compatibility for digital outputs (depending on the value of V <sub>CCO</sub> )                                                     |                                            | LVD                    | S                      |                        |          |

| Differential output voltage swings (assuming $V_{CCO} = 2.25V$ )                                                                          | V <sub>OD</sub>                            | 220                    | 270                    | 350                    | mV       |

| Output levels (assuming $V_{CCO} = 2.25V$ )<br>100 $\Omega$ differentially terminated<br>Logic $\theta$ voltage<br>Logic $\theta$ voltage | V <sub>OL</sub><br>V <sub>OH</sub>         | 1.0<br>1.25            | 1.1<br>1.35            | 1.2<br>1.48            | V<br>V   |

| Output offset voltage (assuming $V_{CCO} = 2.25V$ )<br>100 $\Omega$ differentially terminated                                             | V <sub>os</sub>                            | 1125                   | 1250                   | 1340                   | mV       |

| Output impedance                                                                                                                          | R <sub>O</sub>                             |                        | 50                     |                        | W        |

| Output current (shorted output)                                                                                                           |                                            |                        |                        | 12                     | mA       |

| Output current (grounded output)                                                                                                          |                                            |                        | 30                     |                        | mA       |

| Output level drift with temperature                                                                                                       |                                            |                        | 1.3                    |                        | mV/°C    |

| Digital Input (Serial Interface)                                                                                                          |                                            |                        | 1                      |                        |          |

| Maximum clock frequency (input clk)                                                                                                       | Fclk                                       |                        |                        | 50                     | MHz      |

| Input logical level 0 (clk, mode, data, ldn)                                                                                              |                                            | -0.4                   | 0                      | 0.4                    | V        |

| Input logical level 1 (clk, mode, data, ldn)                                                                                              |                                            | V <sub>CCO</sub> - 0.4 | V <sub>CCO</sub> - 0.4 | V <sub>CCO</sub> + 0.4 | V        |

| Output logical level 0 (cal)                                                                                                              |                                            | -0.4                   | 0                      | 0.4                    | V        |

| Output logical level 1 (cal)                                                                                                              |                                            | V <sub>CCO</sub> - 0.4 | V <sub>cco</sub>       | V <sub>CCO</sub> + 0.4 | V        |

| Maximum output load (cal)                                                                                                                 |                                            |                        |                        | 15                     | pF       |

#### 3.3.1 Timing Diagrams

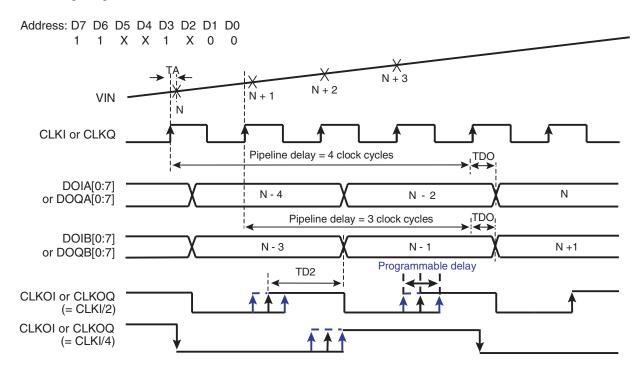

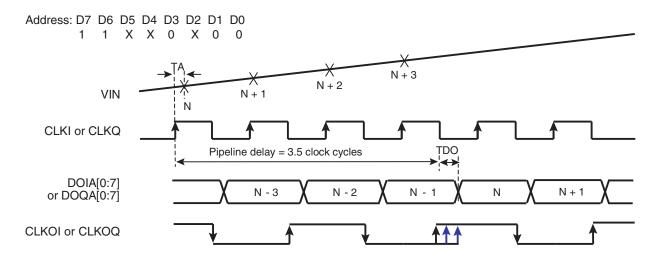

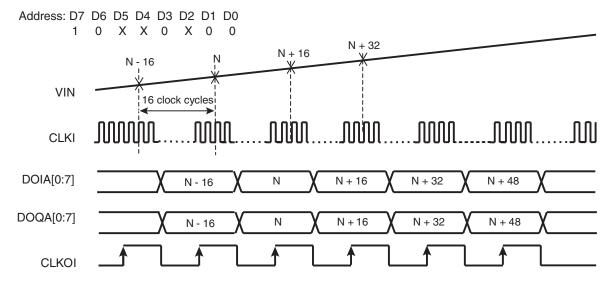

Figure 3-1. Timing Diagram, ADC I or ADC Q, 1:2 DMUX Mode, Clock I for ADC I, Clock Q for ADC Q

Figure 3-2. 1:1 DMUX Mode, Clock I = ADC I, Clock Q = ADC Q

DOIB[0:7] and DOQB[0:7] are high impedance

3-6 AT84AD001-EB - User Guide

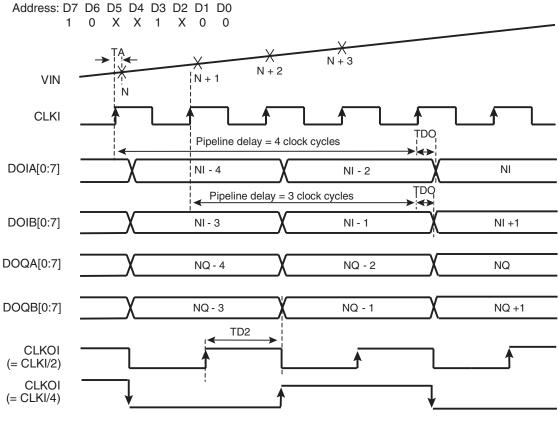

Figure 3-3. 1:2 DMUX Mode, Clock I = ADC I, Clock I = ADC Q

CLKOQ is high impedance

Figure 3-4. 1:1 DMUX Mode, Clock I = ADC I, Clock I = ADC Q

DOIB[0:7] and DOQB[0:7] are high impedance CLKOQ is high impedance

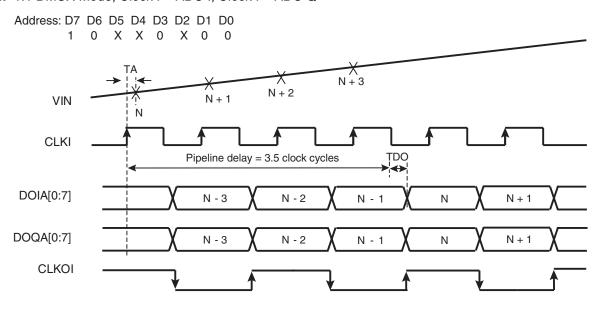

Figure 3-5. 1:2 DMUX Mode, Clock I = ADC I, Clock IN = ADC Q

CLKOQ is high impedance

3-8 AT84AD001-EB - User Guide

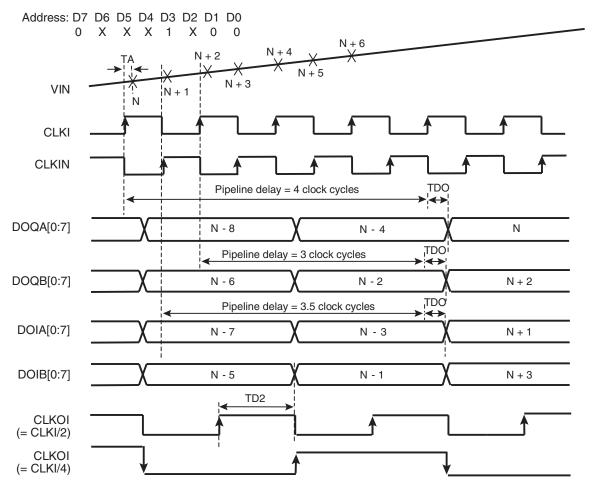

Figure 3-6. 1:1 DMUX Mode, Clock I = ADC I, Clock IN = ADC Q

DOIB[0:7] and DOQB[0:7] are high impedance CLKOQ is high impedance

Figure 3-7. 1:1 DMUX Mode, Decimation Mode Test (1:16 Factor)

DOIB[0:7] and DOQB[0:7] are high impedance CLKOQ is high impedance

Notes: 1. The maximum clock frequency in decimation mode is 750 Msps.

2. Frequency (CLKOI) = Frequency (Data) = Frequency (CLKI)/16.

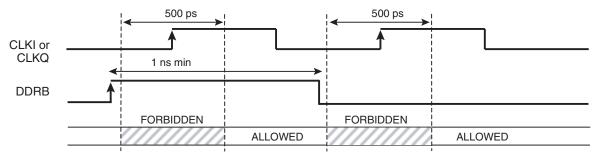

Figure 3-8. Data Ready Reset

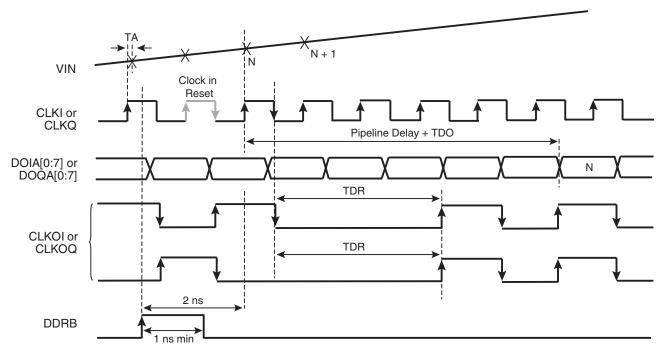

Figure 3-9. Data Ready Reset 1:1 DMUX Mode

Note: The Data Ready Reset is taken into account only 2 ns after it is asserted. The output clock first completes its cycle (if the reset occurs when it is high, it goes low only when its half cycle is complete; if the reset occurs when it is low, it remains low) and then only, remains in reset state (frozen to a low level in 1:1 DMUX mode). The next falling edge of the input clock after reset makes the output clock return to normal mode (after TDR).

3-10 AT84AD001-EB - User Guide

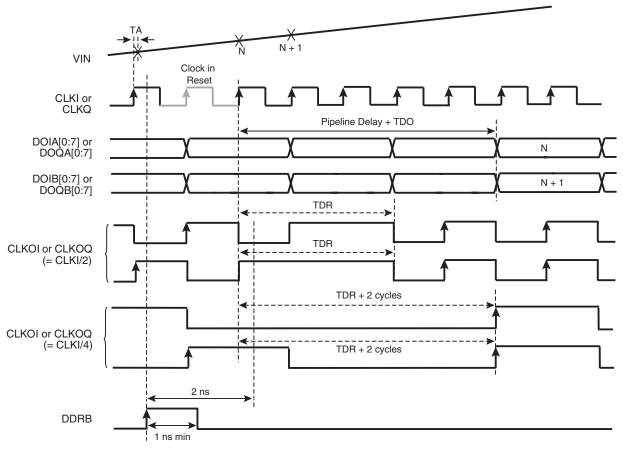

Figure 3-10. Data Ready Reset 1:2 DMUX Mode

#### Notes: 1. In 1:2 DMUX, Fs/2 mode:

The Data Ready Reset is taken into account only 2 ns after it is asserted. The output clock first completes its cycle (if the reset occurs when it is low, it goes high only when its half cycle is complete; if the reset occurs when it is low, it remains high) and then only, remains in reset state (frozen to a high level in 1:2 DMUX Fs/2 mode). The next rising edge of the input clock after reset makes the output clock return to normal mode (after TDR).

2. In 1:2 DMUX, Fs/4 mode:

The Data Ready Reset is taken into account only 2 ns after it is asserted. The output clock first completes its cycle (if the reset occurs when it is high, it goes low only when its half cycle is complete; if the reset occurs when it is low, it remains low) and then only, remains in reset state (frozen to a low level in 1:2 DMUX Fs/4 mode). The next rising edge of the input clock after reset makes the output clock return to normal mode (after TDR).

#### 3.3.2 Digital Coding

Table 3-4. Digital Output Coding (Nominal Setting)

| Differential<br>Analog Input | Voltage Level                                                  | Digital Output<br>I or Q (Binary Coding) | Out-of-range Bit |

|------------------------------|----------------------------------------------------------------|------------------------------------------|------------------|

| > 250 mV                     | > Positive full-scale + 1/2 LSB                                | 11111111                                 | 1                |

| 250 mV<br>248mV              | Positive full-scale + 1/2 LSB<br>Positive full-scale - 1/2 LSB | 11111111                                 | 0<br>0           |

Table 3-4. Digital Output Coding (Nominal Setting) (Continued)

| Differential<br>Analog Input | Voltage Level                   | Digital Output<br>I or Q (Binary Coding) | Out-of-range Bit |

|------------------------------|---------------------------------|------------------------------------------|------------------|

| 1 mV                         | Bipolar zero + 1/2 LSB          | 1000000                                  | 0                |

| -1 mV                        | Bipolar zero - 1/2 LSB          | 0111111                                  |                  |

| -248 mV                      | Negative full-scale + 1/2 LSB   | 00000001                                 | 0                |

| -250 mV                      | Negative full-scale - 1/2 LSB   |                                          | 0                |

| < -250 mV                    | < Negative full-scale - 1/2 LSB | 0000000                                  | 1                |

### 3.4 Test and Control Features

# 3.4.1 3-wire Serial Interface Control Settings

Table 3-5. Control Settings

| Mode             | Characteristics                                                                                                                                                                                                                                                   |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MODE = 1 (2.25V) | 3-wire serial bus interface activated                                                                                                                                                                                                                             |  |

| MODE = 0 (0V)    | 3-wire serial bus interface inactivated Nominal setting:  Dual channel I and Q activated One clock I 0 dB gain DEMUX mode 1:1 DRDA I & Q = 0 ps ISA I & Q = 0 ps FiSDA Q = 0 ps Binary output Decimation test mode OFF Calibration setting OFF Data Ready = Fs /2 |  |

#### 3.4.2 3-wire Serial Interface Address and Data Description

This 3-wire bus is activated with the control bit Mode equal to 1. The length of the word is 19 bits: 16 for the data and 3 for the address. The maximum clock frequency is 50 Msps.

3-12 AT84AD001-EB - User Guide

Table 3-6. 3-wire Serial Interface Address Setting Description

| Address | Setting                                                                                                                                                                                                                                                            |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000     | Standby Gray/binary mode 1:1 or 1:2 DEMUX mode Analog input MUX Clock selection Auto-calibration Decimation test mode Data Ready Delay Adjust                                                                                                                      |

| 001     | Analog gain adjustment  Data7 to Data0: gain channel I Data15 to Data8: gain channel Q  Code 00000000: -1.5 dB  Code 10000000: 0 dB  Code 11111111: 1.5 dB  Steps: 0.011 dB                                                                                        |

| 010     | Offset compensation Data7 to Data0: offset channel I Data15 to Data8: offset channel Q Data7 and Data15: sign bits Code 11111111b: 31.75 LSB Code 10000000b: 0 LSB Code 00000000b: 0 LSB Code 01111111b: -31.75 LSB Steps: 0.25 LSB Maximum correction: ±31.75 LSB |

| 011     | Gain compensation Data6 to Data0: channel I/Q (Q is matched to I) Code 11111111b: -0.315 dB Code 10000000b: 0 dB Code 0000000b: 0 dB Code 0111111b: 0.315 dB Steps: 0.005 dB Data6: sign bit                                                                       |

| 100     | Internal Settling Adjustment (ISA)  Data2 to Data0: channel I  Data5 to Data3: channel Q  Data15 to Data6: 1000010000                                                                                                                                              |

**Table 3-6.** 3-wire Serial Interface Address Setting Description (Continued)

| Address | Setting                                                                                                                                                                                                                                                                                                                         |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 101     | Testability Data3 to Data0 = 0000 Mode S/H transparent OFF: Data4 = 0 ON: Data4 = 1 Data7 = 0 Data8 = 0                                                                                                                                                                                                                         |

| 110     | Built-In Test (BIT)  Data0 = 0 BIT Inactive Data0 = 1 BIT Active  Data1 = 0 Static BIT Data1 = 1 Dynamic BIT  If Data1 = 1Ports BI & BQ = Rising Ramp  Ports AI & AQ = Decreasing Ramp  If Data1 = 0, then Data2 to Data9 = Static Data for BIT  Ports BI & BQ = Data2 to Data9  Ports AI & AQ = NOT (Data2 to Data9)           |

| 111     | Data Ready Delay Adjust (DRDA)  Data2 to Data0: clock I  Data5 to Data3: clock Q  Steps: 140 ps  000:-560 ps  100: 0 ps  111: 420 ps  Fine Sampling Delay Adjustment (FiSDA) on channel Q  Data10 to Data6: channel Q  Steps: 5 ps  Data4: sign bit  Code 11111: -64 ps  Code 10000: 0 ps  Code 00000: 0 ps  Code 01111: 120 ps |

Notes: 1. The Internal Settling Adjustment could change independently of the two analog sampling times (TA channels I and Q) of the sample/hold (with a fixed digital sampling time) with steps of ±50 ps:

Nominal mode will be given by Data2...Data0 = 100 or Data5...Data3 = 100.

Data5...Data3 = 000 or Data2...Data0 = 000: sampling time is -200 ps compared to nominal.

Data2...Data0 = 111 or Data5...Data3 = 111: sampling time is 150 ps compared to nominal.

We recommend setting the ISA to -50 ps to optimize the ADC's dynamic performances.

- 2. The Fine Sampling Delay Adjustment enables you to change the sampling time (steps of ±5 ps) on channel Q more precisely, particularly in the interleaved mode.

- 3. A Built-In Test (BIT) function is available to rapidly test the device's I/O by either applying a defined static pattern to the dual ADC or by generating a dynamic ramp at the output of the dual ADC. This function is controlled via the 3-wire bus interface at the address 110. The maximum clock frequency in dynamic BIT mode is 750 Msps.

- Please refer to "Built-In Test" on page 19 of this section dedicated to the description of this function for more information.

- 4. The decimation mode enables you to lower the output bit rate (including the output clock rate) by a factor of 16, while the internal clock frequency remains unchanged. The maximum clock frequency in decimation mode is 750 Msps.

- 5. The "S/H transparent" mode (address 101, Data4) enables bypassing of the ADC's track/hold. This function optimizes the ADC's performances at very low input frequencies (Fin < 50 MHz).

- 6. In the Gray mode, when the input signal is overflow (that is, the differential analog input is greater than 250 mV), the output data must be corrected using the output DOIR:

If DOIR = 1: Data7 unchanged

Data6 = 0, Data5 = 0, Data4 = 0, Data3 = 0, Data2 = 0, Data1 = 0, Data0 = 0.

3-14 AT84AD001-EB - User Guide

Table 3-7. 3-wire Serial Interface Data Setting Description

| Setting for Address: 000                                                   | D15 | D14 | D13 | D12 | D11 | D10 | <b>D9</b> <sup>(1)</sup> | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|--------------------------|----|----|----|----|----|----|----|----|----|

|                                                                            |     |     |     |     |     |     |                          |    |    |    |    |    |    |    |    |    |

| Full standby mode                                                          | Х   | Х   | Х   | Х   | Χ   | Х   | 0                        | Х  | Х  | Х  | Х  | Х  | Х  | Х  | 1  | 1  |

| Standby channel I <sup>(2)</sup>                                           | Х   | Х   | Х   | Х   | Χ   | Х   | 0                        | Х  | Х  | Х  | Х  | Х  | Х  | Х  | 0  | 1  |

| Standby channel Q <sup>(3)</sup>                                           | Х   | Х   | Х   | Х   | Х   | Х   | 0                        | Х  | Х  | Х  | Х  | Х  | Х  | Х  | 1  | 0  |

| No standby mode                                                            | Х   | Х   | Х   | Х   | Х   | Х   | 0                        | Х  | Х  | Х  | Х  | Х  | Х  | Х  | 0  | 0  |

| Binary output mode                                                         | Х   | Х   | Х   | Х   | Х   | Х   | 0                        | Х  | Х  | Х  | Х  | Х  | Х  | 1  | Х  | Х  |

| Gray output mode                                                           | Х   | Х   | Х   | Х   | Х   | Х   | 0                        | Х  | Х  | Х  | Х  | Х  | Х  | 0  | Х  | Х  |

| DEMUX 1:2 mode                                                             | Х   | Х   | Х   | Х   | Х   | Х   | 0                        | Х  | Х  | Х  | Х  | Х  | 1  | Х  | Х  | Х  |

| DEMUX 1:1 mode                                                             | Х   | Х   | Х   | Х   | Х   | Х   | 0                        | Х  | Х  | Х  | Х  | Х  | 0  | Х  | Х  | Х  |

| Analog selection mode Input I → ADC I Input Q → ADC Q                      | х   | х   | х   | х   | х   | х   | 0                        | х  | х  | х  | 1  | 1  | х  | х  | х  | Х  |

| Analog selection mode Input I → ADC I Input I → ADC Q                      | x   | x   | x   | x   | x   | x   | 0                        | х  | х  | х  | 1  | 0  | х  | х  | х  | X  |

| Analog selection mode Input Q → ADC I Input Q → ADC Q                      | х   | х   | х   | х   | х   | х   | 0                        | х  | Х  | Х  | 0  | Х  | Х  | х  | Х  | Х  |

| Clock Selection mode<br>CLKI → ADC I<br>CLKQ → ADC Q                       | х   | х   | х   | х   | х   | х   | 0                        | х  | 1  | 1  | х  | Х  | Х  | х  | Х  | Х  |

| Clock selection mode<br>CLKI → ADC I<br>CLKI → ADC Q                       | х   | х   | х   | х   | х   | х   | 0                        | х  | 1  | 0  | х  | Х  | Х  | х  | Х  | Х  |

| Clock selection mode<br>CLKI → ADC I<br>CLKIN → ADC Q                      | х   | х   | х   | х   | х   | х   | 0                        | х  | 0  | х  | х  | х  | х  | х  | х  | х  |

| Decimation OFF mode                                                        | Х   | Х   | Х   | Х   | Х   | Х   | 0                        | 0  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  |

| Decimation ON mode                                                         | Х   | Х   | Х   | Х   | Х   | Х   | 0                        | 1  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  |

| Keep last calibration calculated value <sup>(4)</sup> No calibration phase | х   | х   | х   | х   | 0   | 1   | 0                        | х  | х  | х  | х  | х  | х  | х  | х  | х  |

| No calibration phase <sup>(5)</sup><br>No calibration value                | Х   | Х   | Х   | Х   | 0   | 0   | 0                        | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  |

| Start a new calibration phase                                              | х   | х   | х   | х   | 1   | 1   | 0                        | х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  |

**Table 3-7.** 3-wire Serial Interface Data Setting Description (Continued)

| Setting for Address: 000                        | D15 | D14 | D13 | D12 | D11 | D10 | <b>D9</b> <sup>(1)</sup> | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-------------------------------------------------|-----|-----|-----|-----|-----|-----|--------------------------|----|----|----|----|----|----|----|----|----|

| Control wait bit calibration <sup>(6)</sup>     | х   | х   | а   | b   | х   | x   | 0                        | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  |

| In mode DEMUX 1:2<br>FDataReady I & Q =<br>Fs/2 | х   | 0   | х   | х   | х   | x   | 0                        | х  | х  | х  | х  | х  | х  | х  | х  | х  |

| In mode DEMUX 1:2<br>FDataReady I & Q =<br>Fs/4 | х   | 1   | х   | х   | х   | x   | 0                        | х  | х  | х  | х  | х  | х  | х  | х  | х  |

- Notes: 1. D9 must be set to "0"

- 2. Mode standby channel I: use analog input I Vini, Vinib and Clocki.

- 3. Mode standby channel Q: use analog input Q Vinq, Vinqb and Clockq.

- 4. Keep last calibration calculated value no calibration phase: D11 = 0 and D10 = 1. No new calibration is required. The values taken into account for the gain and offset are either from the last calibration phase or are default values (reset values).

- 5. No calibration phase no calibration value: D11 = 0 and D10 = 0. No new calibration phase is required. The gain and offset compensation functions can be accessed externally by writing in the registers at address 010 for the offset compensation and at address 011 for the gain compensation.

- 6. The control wait bit gives the possibility to change the internal setting for the auto-calibration phase:

For high clock rates (>500 Msps) use a = b = 1.

For clock rates >250 Msps and <500 Msps use a=1 and b=0.

For clock rates >125 Msps and <250 Msps use a=0 and b=1.

For low clock rates <125 Msps use a=0 and b=0.

#### 3.4.3 3-wire Serial **Interface Timing** Description

The 3-wire serial interface is a synchronous write-only serial interface made of three wires:

■ sclk: serial clock input

■ sldn: serial load enable input

sdata: serial data input

The 3-wire serial interface gives a write-only access to as many as 8 different internal registers of up to 16 bits each. The input format is always fixed with 3 bits of register address followed by 16 bits of data. The data and address are entered with the Most Significant Bit (MSB) first.

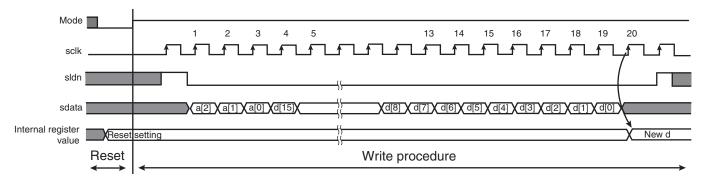

The write procedure is fully synchronous with the rising clock edge of "sclk" and described in the write chronogram hereafter:

- "sldn" and "sdata" are sampled on each rising clock edge of "sclk" (clock cycle).

- "sldn" must be set to 1 when no write procedure is performed.

- A minimum of one rising clock edge (clock cycle) with "sldn" at 1 is required for a correct start of the write procedure.

- A write starts on the first clock cycle with "sldn" at 0. "sldn" must stay at 0 during the complete write procedure.

- During the first 3 clock cycles with "sldn" at 0, 3 bits of the register address from MSB (a[2]) to LSB (a[0]) are entered.

- During the next 16 clock cycles with "sldn" at 0, 16 bits of data from MSB (d[15]) to LSB (d[0]) are entered.

3-16 AT84AD001-EB - User Guide

- An additional clock cycle with "sldn" at 0 is required for parallel transfer of the serial data d[15:0] into the addressed register with address a[2:0]. This gives 20 clock cycles with "sldn" at 0 for a normal write procedure.

- A minimum of one clock cycle with "sldn" returned at 1 is requested to close the write procedure and before the interface is ready for a new write procedure. Any clock cycle where "sldn" is at 1 *before* the write procedure is completed interrupts this procedure and no further data transfer to the internal registers is performed.

- Additional clock cycles with "sldn" at 0 after the parallel data transfer to the register (done at the 20th consecutive clock cycle with "sldn" at 0) do not affect the write procedure and are ignored.

It is possible to have only one clock cycle with sldn at 1 between two following write procedures.

■ 16 bits of data must always be entered even if the internal addressed register has less than 16 bits. Unused bits (usually MSBs) are ignored. Bit signification and bit positions for the internal registers are detailed in Section 3.4.1 and Section 3.4.2.

To reset the registers, the Pin mode can be used as a reset pin for chip initialization, even when the 3-wire serial interface is used.

Figure 3-11. Write Chronogram

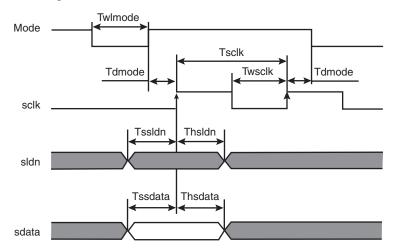

Figure 3-12. Timing Definition

Table 3-8. Timing Description

|         |                                                                   |     | Value |     | Unit |

|---------|-------------------------------------------------------------------|-----|-------|-----|------|

| Name    | Parameter                                                         | Min | Тур   | Max | Unit |

| Tsclk   | Period of Sclk                                                    | 20  |       |     | ns   |

| Twsclk  | High or low time of sclk                                          | 5   |       |     | ns   |

| Tssldn  | Setup time of sldn before rising edge of sclk                     | 4   |       |     | ns   |

| Thsldn  | Hold time of sldn after rising edge of sclk                       | 2   |       |     | ns   |

| Tssdata | Setup time of sdata before rising edge of sclk                    | 4   |       |     | ns   |

| Thsdata | Hold time of sdata after rising edge of sclk                      | 2   |       |     | ns   |

| Twlmode | Minimum low pulse width of mode                                   | 5   |       |     | ns   |

| Tdmode  | Minimum delay between an edge of mode and the rising edge of sclk | 10  |       |     | ns   |

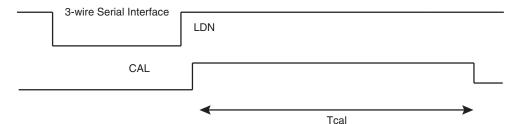

### 3.4.4 Calibration Description

The AT84AD001B offers the possibility of reducing offset and gain matching between the two ADC cores.

An internal digital calibration may start right after the end of the loading of the 3-wire serial interface (using data D12 of the 3-wire serial interface with address 000).

The beginning of calibration disables the two ADCs and a standard data acquisition is performed.

The output bit CAL goes to a high level during the entire calibration phase. When this bit returns to a low level, the two ADCs are calibrated with offset and gain and can be used again for a standard data acquisition .

If only one channel is selected (I or Q) the offset calibration duration is divided by two and no gain calibration between the two channels is necessary .

Figure 3-13. Internal Calibration Timing

The Tcal duration is a multiple of the clock frequency ClockI (master clock). Even if a dual clock scheme is used during calibration ClockQ will not be used.

The control wait bits (D13 and D14) give the possibility of changing the calibration's setting depending on the clock's frequency:

- For high clock rates (> 500 Msps) use a = b = 1, Tcal = 10112 clock I periods.

- For clock rates > 250 Msps and < 500 Msps use a = 1, b = 0, Tcal = 6016 clock I periods.

- For clock rates > 125 Msps and < 250 Msps use a = 0, b = 1 ,Tcal = 3968 clock I periods.

3-18 AT84AD001-EB - User Guide

■ For low clock rates (< 125 Msps) use a = 0, b = 0, Tcal = 2944 clock I periods.

The calibration phase is necessary when using the AT84AD001B in interlace mode, where one analog input is sampled at both ADC cores on the common input clock's rising and falling edges. This operation is equivalent to converting the analog signal at twice the clock frequency.

Table 3-9. Matching Between Channels

|                                                              |     | Value |     |      |  |  |  |

|--------------------------------------------------------------|-----|-------|-----|------|--|--|--|

| Parameter                                                    | Min | Тур   | Max | Unit |  |  |  |

| Gain error (single channel I or Q) without calibration       |     | 0     |     | LSB  |  |  |  |

| Gain error (single channel I or Q) with calibration          | -2  | 0     | 2   | LSB  |  |  |  |

| Offset error (single channel I or Q) without calibration     |     | 0     |     | LSB  |  |  |  |

| Offset error (single channel I or Q) with calibration        | -2  | 0     | 2   | LSB  |  |  |  |

| Mean offset code without calibration (single channel I or Q) |     | 127.5 |     |      |  |  |  |

| Mean offset code with calibration (single channel I or Q)    | 126 | 127.5 | 129 |      |  |  |  |

During the ADC's auto-calibration phase, the dual ADC is set with the following:

- Decimation mode ON

- 1:1 DMUX mode

- Binary mode

Any external action applied to any signal of the ADC's registers is inhibited during the calibration phase.

## 3.4.5 Gain and Offset Compensation Functions

It is also possible for the user to have external access to the ADC's gain and offset compensation functions:

- Offset compensation between I and Q channels (at address 010)

- Gain compensation between I and Q channels (at address 011)

To obtain manual access to these two functions, used to set the offset to middle code 127.5 and to match the gain of channel Q with that of channel I (if only one channel is used, the gain compensation does not apply), it is necessary to set the ADC to "manual" mode by writing 0 at bits D11 and D10 of address 000.

#### 3.4.6 Built-In Test

A Built-In Test (BIT) function is available to allow rapid testing of the device's I/O by either applying a defined static pattern to the ADC or by generating a dynamic ramp at the ADC's output. The dynamic ramp can be used with a clock frequency of up to 750 Msps. This function is controlled via the 3-wire bus interface at address 101.

- The BIT is active when Data0 = 1 at address 110.

- The BIT is inactive when Data0 = 0 at address 110.

- The Data1 bit allows you to choose between static mode (Data1 = 0) and dynamic mode (Data1 = 1).

When the static BIT is selected (Data1 = 0), it is possible to write any 8-bit pattern by defining the Data9 to Data2 bits. Port B then outputs an 8-bit pattern equal to Data9 ... Data2 and Port A will output an 8-bit pattern equal to NOT (Data9 ... Data2).

#### Example:

#### Operating Characteristics and Procedures

Address = 110

Data =

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| Х   | Х   | Х   | Х   | Х   | X   | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  |

One should then obtain 01010101 on port B and 10101010 on port A.

When the dynamic mode is chosen (Data1 = 1) port B outputs a rising ramp while port A outputs a decreasing one.

#### 3.4.7 Decimation Mode

The decimation mode is provided to enable rapid testing of the ADC at a maximum clock frequency of 750 Msps. In the decimation mode, one data out of 16 is output, thus leading to a maximum output rate of 46.875 Msps.

3-20 AT84AD001-EB - User Guide

### e<sub>2</sub>v

### **Section 4**

### **Software Tools**

#### 4.1 Overview

The dual 8-bit evaluation user interface software is a Visual C++<sup>®</sup> compiled graphical interface that does not require a licence to run on a Windows<sup>®</sup> NT<sup>®</sup> and Windows<sup>®</sup> 2000/98/XP<sup>®</sup> PC.

The software uses intuitive push-buttons and pop-up menus to write data from the hardware.

#### 4.2 Configuration

The advised configuration for Windows® 98 is:

- PC with Intel® Pentium® Microprocessor of over 100 MHz

- Memory of at least 24 Mo

For other versions of Windows® OS, use the recommended configuration from Microsoft®.

Note: Two COM ports are necessary to use two boards simultaneously.

#### 4.3 Getting Started

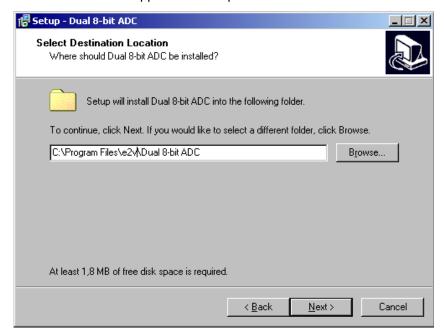

1. Install the ADC dual 8-bit 1 Gsps application on your computer by launching the Dual8bitADC\_2.x.x.exe installer (please refer to the latest version available).

The following window appears:

Figure 4-1. Dual 8-bit ADC Setup Window

2. Click on Yes to start the Dual 8-bit application.

The following screen is displayed:

Figure 4-2. Dual 8-bit ADC Application Setup Wizard Window

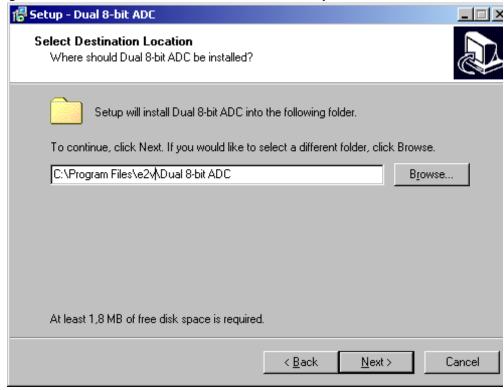

3. Select a destination directory.

Figure 4-3. Dual 8-bit ADC Select Destination Directory Window

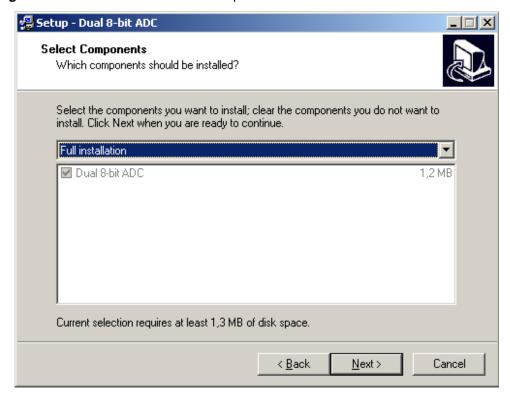

4. Select components (choose Full installation)

4-2

Figure 4-4. Dual 8-bit ADC Select Component Window

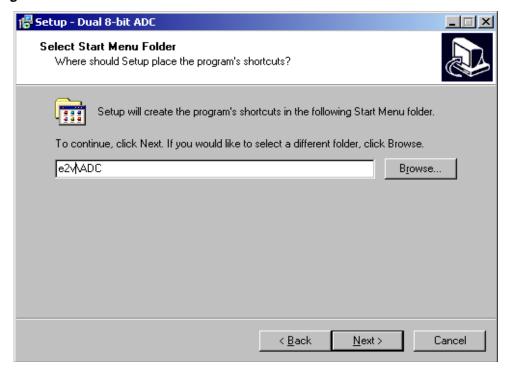

5. Select the Start Menu.

Figure 4-5. Dual 8-bit ADC Select Start Menu Window

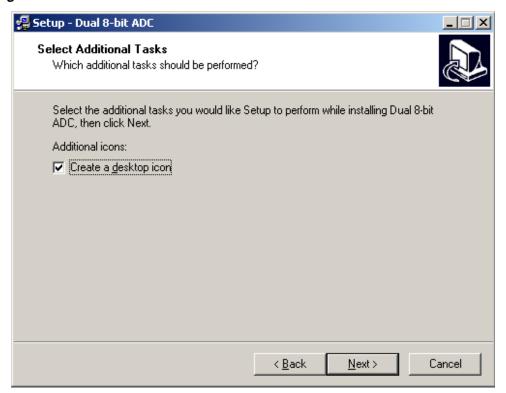

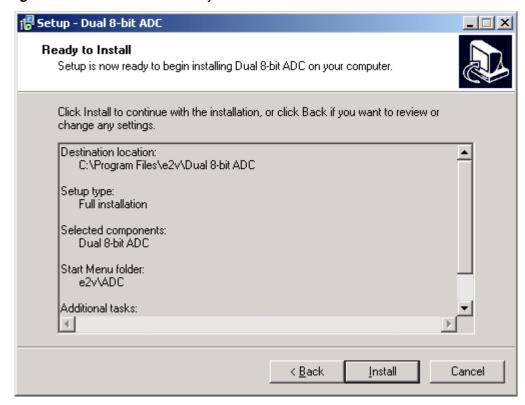

6. Select Additional Tasks

Figure 4-6. Dual 8-bit ADC Select Additional Tasks Window

7. Verify the installation configuration.

4-4 AT84AD001-EB - User Guide

Figure 4-7. Dual 8-bit ADC Ready to Install Window

8. If you agree with the installation configuration, press the *Install* button.

The software installation is now complete.

Completing the Dual 8-bit ADC Setup Wizard

Setup has finished installing Dual 8-bit ADC on your computer. The application may be launched by selecting the installed icons.

Click Finish to exit Setup.

| Launch Dual 8-bit ADC |

Figure 4-8. Dual 8-bit ADC Completing Setup Wizard Window

After the installation, you can launch the interface with the following file:

C:\Program Files\e2v\Dual 8-bit ADC\Dual8BitADC.exe

4-6 AT84AD001-EB - User Guide

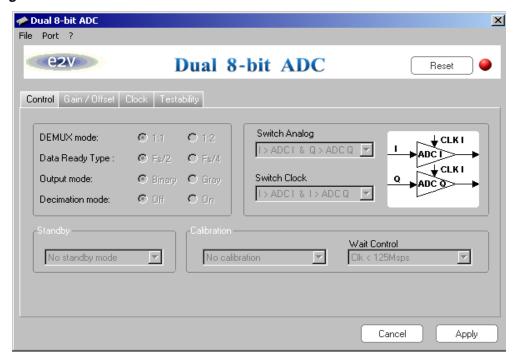

The window shown in Figure 4-10 is displayed.

Figure 4-9. Dual 8-bit ADC User Interface Window

Note: If the Dual 8-bit ADC Application board is not connected or not switched on, a red LED light appears to the right of the reset button as shown in Figure 4-10, and the application is grayed out.

If this is the case, you should:

Check your connection and restart the application.

If the serial interface is not active, the LED appears orange and the application is again grayed out.

Figure 4-10. Dual 8-bit ADC User Interface Window

9. Turn ON the demo board. The application should start and the LED turns green.

Figure 4-11. Dual 8-bit ADC User Interface Window

AT84AD001-EB - User Guide 4-7

### 4.3.0.1 Troubleshooting

- 1. Check that you own rights to write in the directory.

- 2. Check for the available disk space.

- 3. Check that at least one RS-232 serial port is free and properly configured.

- 4. Check that the serial port and DB9 connector are properly connected.

- 5. Check that all supplies are properly powered on.

- 6. Check that the serial mode is active (green LED on).

The serial port configuration should be as follows:

■ Bit rate: 19200

■ Data coding: 8 bits

■ 1 start bit, 1 stop bit

■ No parity check

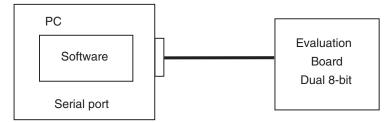

Figure 4-12. Dual 8-bit ADC User Interface Hardware Implementation

- 1. Use an RS-232 port to send data to the ADC.

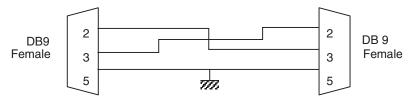

- 2. Connect the crossed DB9 (F/F) cable between your PC and your evaluation board as illustrated in Figure 4-14.

Figure 4-13. Crossed Cable

## 4.4 Installation Software

When the application is started, it automatically checks all RS-232 ports available on the computer and tries to find the evaluation board connected to the RS-232 port.

4-8 AT84AD001-EB - User Guide

0819E-BDC-05/11/07

nal 8-bit ADC 🌪 X File | Port | ? COM1 Dual 8-bit ADC COM2 Reset Control Gain / Offset Clock Testability Switch Analog DEMUX mode: © 1:1 O 1:2 I>ADCI & Q>ADCQ Data Ready Type: ♠ Fs/2 C Fs/4 C Binary C Gray Switch Clock Output mode: ANC Ø I > ADCI & I > ADCQ Decimation mode: ○ Off O On Wait Control No standby mode No calibration Clk < 125Msps Cancel Apply

Figure 4-14. Dual 8-bit ADC User Interface Port Menu

The port menu shows all available ports on your computer. The port currently used has a check mark to its left. By clicking another port item, the application tries to connect to an evaluation board via the selected port. If a board is successfully detected on the new port, the LED turns green (or orange depending on the serial interface switch) and the new port becomes active. If the application is not able to find a board on this port, an error message is displayed and the LED turns red.

### 4.5 Operating Modes

#### 4.5.1 Overview

The software provides a graphical user interface to configure the ADC. Push buttons, pop-up menus and capture windows enable easy activation of the following:

- Control mode

- Switch analog and switch clock

- Standby

- Calibration and wait controls

- Gain and balance controls

- Offset

- SDA balance

Always press the *Apply* button to validate a command:

AT84AD001-EB - User Guide 4-9

Pressing the Cancel button restores the last settings sent with the Apply button.

The *Reset* button enables re-configuration of the ADC (Mode 0):

#### 4.5.2 Control Mode

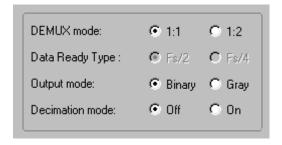

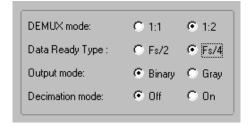

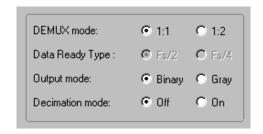

The control mode enables you to control the DEMUX, the output, the decimation and set the Data Ready Type modes. Figure 4-16 shows the normal mode configuration:

Figure 4-15. Normal Mode Configuration

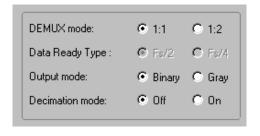

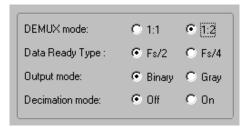

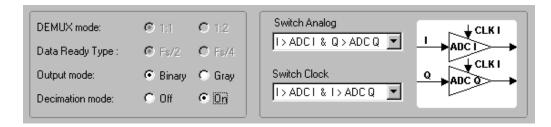

#### 4.5.3 DEMUX Mode

Figure 4-16. DEMUX Mode Configuration (1:1 or 1:2)

Note: In DEMUX mode 1:1, the DataReady type is fixed to Fs/2 by design.

### 4.5.4 Data Ready Type

Figure 4-17. Data Ready Type Fs/2 or Fs/4

### 4.5.5 Output Mode

Figure 4-18. Output Mode Configurable in Binary or Gray

### 4.5.6 Decimation Mode

Figure 4-19. Decimation OFF or ON (Division of 16)

Note: The maximum clock frequency in Decimation mode is 750 Msps.

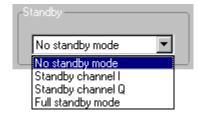

### 4.5.7 Standby Mode

Figure 4-20. Standby Mode Pop-up Menu

AT84AD001-EB - User Guide 4-11

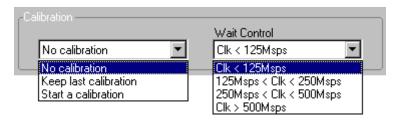

#### 4.5.8 Calibration Mode

Figure 4-21. Calibration Mode Pop-up Menu

Note: Do not forget to configure the "Wait Control" parameter for a calibration phase.

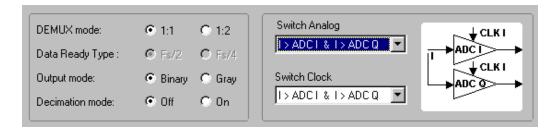

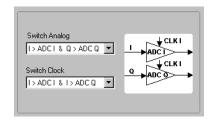

## 4.5.9 Analog Input Signal Selection

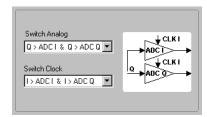

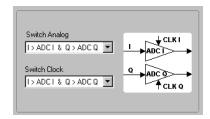

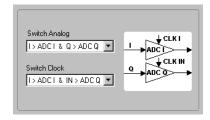

Figure 4-22. Switch Analog Pop-up Menus

Input I > ADC I and Input Q > ADC Q (Normal Mode)

Input I > ADC I and Input I > ADC Q

Input Q > ADC I and Input Q > ADC Q

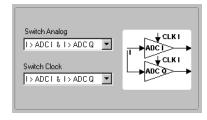

### 4.5.10 Clock Selection

Figure 4-23. Switch Clock Pop-up Menus

Clock I > ADC I and Clock I > ADC Q (Normal Mode)

Clock I > ADC I and Clock Q > ADC Q

Clock I > ADC I and Clock IN > ADC Q (Interlacing Mode)

### 4.5.11 Gain Adjust

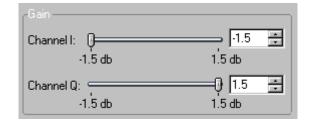

Figure 4-24. Gain of ADC I and ADC Q (-1.5 to 1.5 dB)

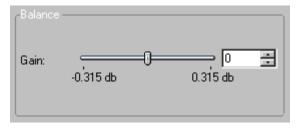

### **4.5.12 Gain Compensation** *Figure 4-25.* Gain Balance (Compensation of Channel Q) - 0.315 to 0.315 dB

### 4.5.13 Offset Adjust

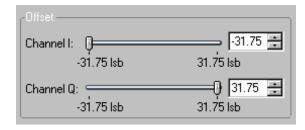

Figure 4-26. Offset of ADC I and ADC Q (-31.75 to 31.75 LSB)

AT84AD001-EB - User Guide 4-13

## 4.5.14 Internal Setting Adjustment

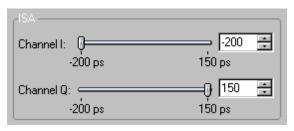

Figure 4-27. ISA of ADC I and ADC Q (-200 ps to 150 ps)

Note: We recommended setting the ISA to -50 ps to optimize the ADC's dynamic performances.

## 4.5.15 Data Ready Delay Adjust

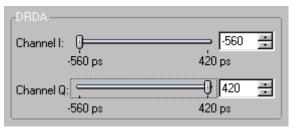

Figure 4-28. DRDA of ADC I and ADC Q (-560 ps to 420 ps)

## 4.5.16 Fine Sampling Delay Adjust

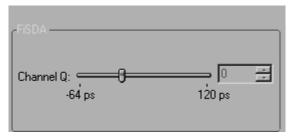

Fine Sampling Delay Figure 4-29. FiSDA of ADC I and ADC Q (-64 ps to 120 ps)

### 4.5.17 Test Mode

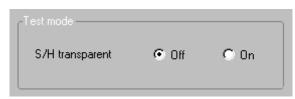

Figure 4-30. Test Mode

Note: This mode may be used for low input frequencies to optimize the dynamic performances (Fin <50 MHz).

### 4.5.18 Built-In Test

Figure 4-31. Built-in Test Configuration Windows

**Built-In Test Inactive**

Built-In Test Active (Static BIT)

Built-In Test Active (Dynamic BIT)

Note: The maximum clock frequency in Dynamic BIT mode is 750 Msps.

AT84AD001-EB - User Guide 4-15

### Software Tools

4-16 AT84AD001-EB - User Guide

### **Section 5**

# **Application Information**

### 5.1 Analog Input

The analog inputs  $(V_{INI} \text{ or } V_{INQ})$  are entered in differential mode thanks to an RF transformer.

The RF transformer provides an excellent solution to convert a single-ended signal to a fully differential signal. In this example we used a TP-101 RF transformer 500 kHz - 1.5 GHz to create a differential input signal.

The analog inputs are DC coupled to ground. The transmission line must be routed to  $50\Omega$  impedance signal traces.

Figure 5-1. Analog Input Implementation

AT84AD001-EB - User Guide 5-1

Both ADCs can convert the same analog input signal I or Q. The analog input switch is configurable via a serial interface address 000 bit 4 and bit 5.

Table 5-1. Analog Input Switch Settings

| Setting for Address: 000                                                                                                                  | D5 | D4 |

|-------------------------------------------------------------------------------------------------------------------------------------------|----|----|

| Analog selection mode $ \begin{array}{l} \text{Input I} \rightarrow \text{ADC I} \\ \text{Input Q} \rightarrow \text{ADC Q} \end{array} $ | 1  | 1  |

| Analog selection mode Input I $\rightarrow$ ADC I Input I $\rightarrow$ ADC Q                                                             | 1  | 0  |

| Analog selection mode Input $Q \to ADC I$ Input $Q \to ADC Q$                                                                             | 0  | x  |

### 5.2 Clock Input

The clock inputs can be entered in differential or single-ended mode with no performance degradation. The clock input signals enter in CLK (in-phase input), while pin CLKB (inverted phase) is terminated by a  $50\Omega$  load termination. The transmission lines are routed at  $50\Omega$  impedance signal traces.

Figure 5-2. Clock Input Implementation

The analog input switch is configurable via the serial interface at address 000 on bit 7 and bit 6.

5-2 AT84AD001-EB - User Guide

0819E-IMAGE-05/11/07

Table 5-2. Clock Input Switch Settings

| Setting for Address: 000 | D7 | D6 |

|--------------------------|----|----|

| Clock selection mode     | 1  | 1  |

| Clock selection mode     | 1  | 0  |

| Clock selection mode     | 0  | x  |

## 5.3 Data Output Termination

All digital outputs are  $50\Omega$  differentially terminated via a 1 nF chip capacitor, as shown in Figure 5-3.

Figure 5-3. Digital Output Termination

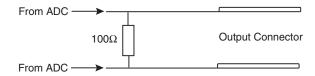

Note: It is possible to use a  $100\Omega$  differentially terminated output.

**Figure 5-4.**  $100\Omega$  Differential Digital Output Termination

The data output format is configurable via the serial interface at address 000 on bit 2.

Table 5-3. Digital Output Format Settings

| Setting for Address: 000 | D2 |

|--------------------------|----|

| Binary output mode       | 1  |

| Gray output mode         | 0  |

AT84AD001-EB - User Guide 5-3

## 5.4 Control Function Settings

### 5.4.1 ADC Gain Adjust

The gain is adjustable via the serial interface at addresses 001 and 011. The channel I and Q gains can be configured separately using address 001 (with a variation of 1.5 dB to -1.5 dB). The channel Q gain can be configured in correlation with channel I using address 011.

Table 5-4. Analog Gain Settings

| Address | Setting                                                                                                                                 |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

|         | Gain compensation                                                                                                                       |  |

| 011     | Data6Data0: channel I/Q<br>Steps: 0.005 dB<br>Data6: sign bit                                                                           |  |

|         | Analog gain adjustment :                                                                                                                |  |

| 001     | Data7Data0: Gain channel I Data15Data8: Gain Channel Q Code 00000000: -1.5 dB Code 10000000: 0 dB Code 11111111: 1.5 dB Steps: 0.011 dB |  |

### 5.4.2 ADC Offset Adjust

The offset can be compensated via the serial interface address 010.

The offset of channel I and Q can be configured separately.

Variation 31.75 LSB to -31.75 LSB.

Table 5-5. Offset Settings

| Address | Setting                                                                                                                                |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------|--|

|         | Offset compensation                                                                                                                    |  |

| 010     | Data7Data0 : offset channel I Data15Data8: offset channel Q Data7 and Data15: sign bits Steps: 0.25 LSB Maximum correction: ±31.75 LSB |  |

5-4 AT84AD001-EB - User Guide

0819E-IMAGE-05/11/07

## 5.4.3 ADC Gain Compensation

The gain can be compensated via the serial interface at address 011. The gain of channel I and Q can be configured separately with a variation of -0.315 dB to +0.315 dB.

Table 5-6. Gain Compensation Settings

| Address | Setting                                                                                                                                             |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

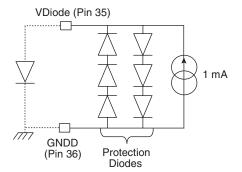

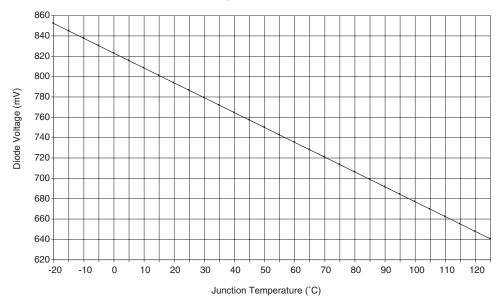

|         | Gain compensation                                                                                                                                   |  |