# e2v

# Quad ADC EV8AQ160

# **Application Note**

## 1. Introduction

This application note aims at providing you some recommendations to implement the EV8AQ160 Quad 8-bit 1.25 Gsps ADC in your system.

It first presents the ADC input/output interfaces and then provides some recommendations as regards the device settings and board layout to obtain the best performance of the device.

This document applies to the:

• EV8AQ160 8-bit 1.25 Gsps ADC

## 2. EV8AQ160 ADC Input Terminations

## 2.1 Clock Input

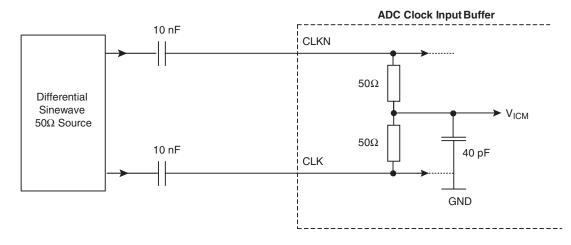

It is recommended to drive the Quad ADC input clock in a differential way in order to optimize the performance of the ADC and minimize the injection of noise in the die ground.

As the clock input common mode is 2.5V, it is recommended to AC couple the clock signal, as illustrated in Figure 2-1.

## Figure 2-1. EV8AQ160 ADC Clock Input Termination Scheme

## 2.2 Analog Input

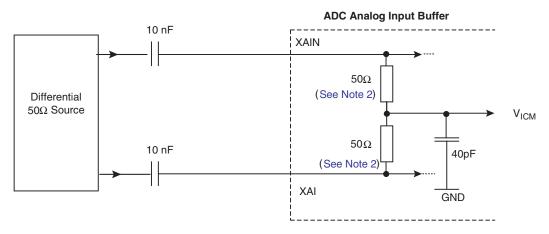

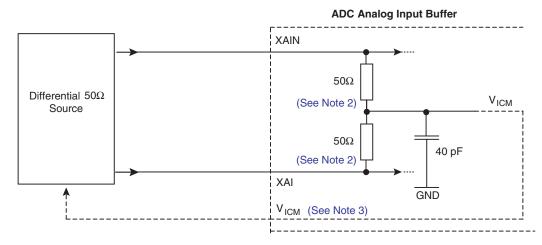

It is highly recommended to use the analog input (any channel) in differential mode (the performance can be decreased if the ADC is used in single-ended mode).

## 2.2.1 Differential Analog Input

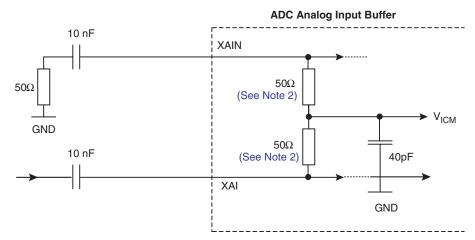

When used in differential mode, the analog input can be either DC or AC coupled as described in Figure 2-2 and Figure 2-3.

## Figure 2-2. Differential Analog Input Implementation (AC Coupled)

Note: 1. X = A, B, C or D.

- 2. The  $50\Omega$  terminations are implemented on-chip and can be fine tuned (TRIMMER register at address 0x13).

- 3.  $V_{ICM} = 1.8V.$

## Figure 2-3. Differential Analog Input Implementation (DC Coupled)

Note: 1. X = A, B, C or D.

- 2. The 50 $\Omega$  terminations are implemented on-chip and can be fine tuned (TRIMMER register at address 0x13).

- 3.  $V_{ICM} = 1.8V$ . The VICM signal is output from the ADC to provide the common mode to the front-end.

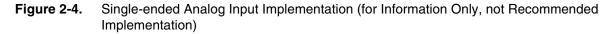

#### 2.2.2 Single-ended Analog Input

When used in single-ended mode (not recommended implementation), the analog input has to be AC coupled as described in Figure 2-4.

Note: 1. X = A, B, C or D.

- 2. The  $50\Omega$  terminations are implemented on-chip and can be fine tuned (TRIMMER register at address 0x13).

- 3.  $V_{ICM} = 1.8V.$

# 3. EV8AQ160 ADC Output Terminations

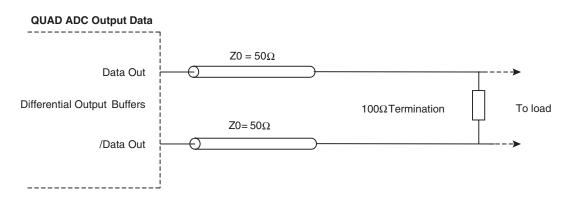

The digital outputs are LVDS compatible. They have to be  $100\Omega$  differentially terminated.

**Figure 3-1.** Differential Digital Outputs Terminations (100Ω LVDS)

# 4. EV8AQ160 ADC Hardware Signals

## 4.1 RESET Signals

## 4.1.1 ADC Synchronization Signal (SYNC, SYNCN)

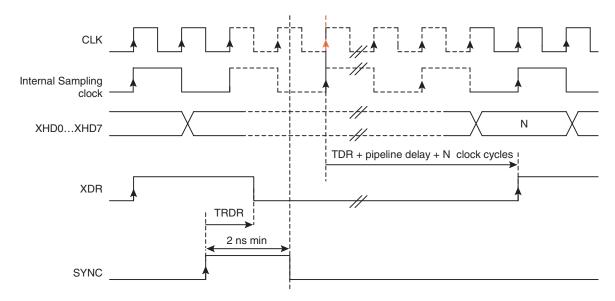

The SYNC, SYNCN signal has LVDS electrical characteristics. It is active high and should last at least 2 ns to work properly.

Once asserted, it has an effect on the output clock signals which are then forced to LVDS low level as described in Figure 4-1. During reset, the output data are not refreshed.

Once de-asserted, the output clock signals restart toggling after (TDR + pipeline delay) + N clock cycles, where N can be selected via the Serial Peripheral Interface at address 0x06 (from 0 to 15).

This SYNC signal can be used to ensure the synchronization of multiple ADCs.

Note: 1. In DMUX 1:2 mode, the SYNC, SYNCN signal also resets the clock divider for the DMUX.

2. In decimation mode, the SYNC, SYNCN signal also resets the clock dividers for decimation, therefore. data outputs are not refreshed or may be corrupted when SYNC, SYNCN is active.

Figure 4-1. SYNC Timing in Four-channel Mode, 1:1 DMUX Mode (for Each Channel)

Note: X refers to A, B, C and D.

## 4.1.2 Digital Reset (RSTN)

This is a global hardware Reset for the digital part. It is active low.

- Note: 1. There are two ways to reset the Quad 8-bit 1.25 Gsps ADC:

- 2. By asserting low the RSTN primary pad (hardware reset)

- 3. By writing a "1" in the bit SWRESET of the SWRESET register through the SPI (software reset)

Both ways will clear all configuration registers to their reset values.

## 4.2 DIODE

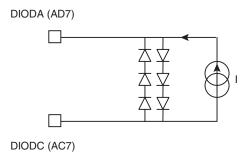

DIODEA, DIODEC: two pins are provided so that the diode can be probed using standard temperature sensors.

It is recommended to protect the diode using 2 x 3 head-to-tail diodes as illustrated in Figure 4-2 (note that if a standard temperature sensor is used, the protection diodes are not necessary).

Figure 4-2. Protection Diodes for the Junction Temperature Monitoring Diode

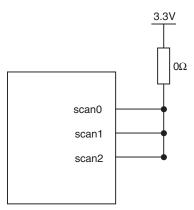

## 4.3 SCAN Signals

The scan signals (pins AD14, AC14, AD15) should be connected to 3.3V as illustrated in Figure 4-3.

Figure 4-3. Scan Signals Recommended Implementation

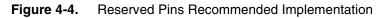

## 4.4 Test signals

The reserved signals (trigp pin AD10, trign pin AC10, tdreadyp pin AD8, tdreadyn pin AC8, tdcop pin AD9 and tdcon pin AC9) should be connected as described in Figure 4-4.

## 5. SPI

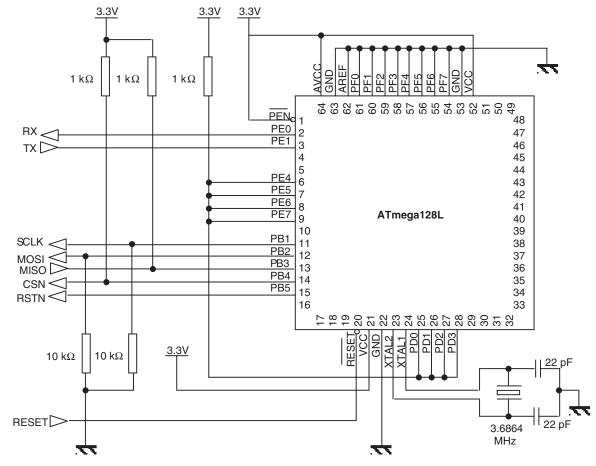

Atmel ATmega128L AVR can be used to drive the SPI of Atmel EV8AQ160 Quad 8-bit 1.25 Gsps ADC.

In this first section, a simple configuration for the interfacing of the AVR with the ADC is provided.

Note: All the information contained in this document concerning the AVR complies with the version available at the date the document was created. It should be checked versus the current version available before design.

## 5.1 EV8AQ160 8-bit 1.25 Gsps ADC SPI

Five signals of the EV8AQ160 Quad 8-bit 1.25 Gsps ADC can be driven via the ATmega128L AVR:

- The CSN signal (pin AC16): used in the ADC to activate the 3-wire serial interface

- The SCLK signal (pin AD16): input clock for the SPI

- The MISO signal (pin AC17): master input slave output of the SPI (output of the ADC)

- The MOSI signal (pin AD17): master output slave input of the SPI (input for the ADC)

- The RSTN signal (pin AC15): external reset for the SPI

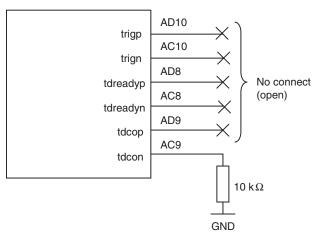

#### 5.1.1 CSN Signal

This signal should be pulled up to  $V_{CC}$  = 3.3V via a pull-up resistor (1 k $\Omega$  to 4.7 k $\Omega$ ) so that it is not activated by default.

#### Figure 5-1. CSN Implementation

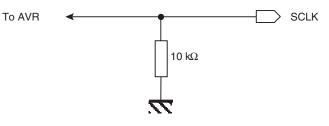

## 5.1.2 SCLK Signal

This signal should be pulled down to ground via a 10 k $\Omega$  resistor so that it is not activated by default.

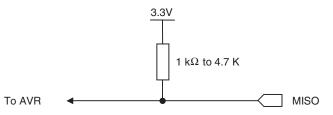

#### 5.1.3 MISO Signal

This signal should be pulled up to  $V_{CC}$  = 3.3V via a pull-up resistor (1 k $\Omega$  to 4.7 k $\Omega$ ) so that it is not activated by default

### Figure 5-2. MISO Implementation

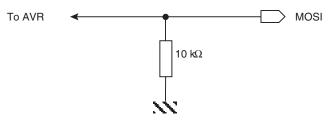

## 5.1.4 MOSI Signal

This signal should be pulled down to ground via a 10 k $\Omega$  resistor so that it is not activated by default.

## Figure 5-3. MOSI implementation

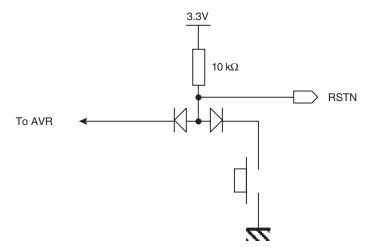

## 5.1.5 RSTN Signal

This signal should be pulled up to  $V_{CC}$  = 3.3V via a 10 k $\Omega$  resistor so that it is not activated by default.

As this reset is normally a hardware reset, it can be useful to allow an external reset by a push button for example. In order to work out the conflict between the AVR and the push button, diodes can be used as illustrated in Figure 5-4.

## Figure 5-4. RSTN Implementation (Command via the AVR and via a Push Button)

## 5.1.6 ATmega128L 8-bit Microcontroller In-System Programmable Flash

Because Port B provides the pins for the SPI channel, this is the port chosen for the four signals of the ADC SPI as well as the RSTN signal:

- CSN to PB4 (OC0 = Output Compare and PWM Output for Timer/Counter0)

- SCLK to PB1 (SCK = SPI bus serial clock)

- MOSI to PB2 (MOSI = SPI bus Master Output/Slave Input)

- MISO to PB3 (MISO = SPI bus Master Input /Slave Output)

- RSTN to PB5 (OC1A = Output Compare and PWM Output A for Timer/Counter1)

The other pins PB0 ( $\overline{SS}$ ), PB6 (OC1B) and PB7 (OC2/OC1C) can be left floating (open).

Pin PB3 (MISO = SPI Bus Master Input/Slave Output) needs to be pulled up to 3.3V via a 1 k $\Omega$  resistor in order to be forced to a high level and not left open.

Pins SPICLOCK = PB1 and SPIDATA = PB2 need to be pulled down to ground via a 10 k $\Omega$  resistor to be forced to low level (inhibition of the SPI during reset of the microcontroller).

Pin SLE = PB4 (OC0 = Output Compare and PWM Output for Timer/Counter0) needs to be pulled up to 3.3V via a 3.3 k $\Omega$  (or 1 k $\Omega$  if the power consumption is not critical) resistor in order to protect the line during reset of the microcontroller (in which phase the signal becomes an input).

Ports A and C of the AVR can be left floating (open) but have to be internally configured with pull-ups.

For Port D, pins PD7, PD6, PD5 and PD4 can be left unused (open) but have to be internally configured with pull-ups. Pins PD3, PD2, PD1 and PD0 have to be pulled up to 3.3V via a 1 k $\Omega$  resistor in order to inhibit external interrupts.

For port E, pins PE3 and PE2 can be left unused (open) but have to be internally configured with pullups. Pins PE7, PE6, PE5 and PE4 have to be pulled up to 3.3V via a 1 k $\Omega$  resistor in order to inhibit external interrupts.

PE1 and PE0 can be used as the Programming Data Output (TX) and Input (RX) to be connected to the TX and RX of the system (in the case of the EV8AQ160-EB evaluation board, these signals are sent to the PC via an RS232 port).

All the pins of Port F have to be connected to ground so that they are in a known fixed state (no internal pull-down available for these pins).

All pins of Port G can be left floating (open).

Finally, the five remaining signal pins are to be connected as follows:

- PEN = programming enable pin for the SPI serial programming mode, to be connected to V<sub>CC</sub> = 3.3V to activate the SPI programming mode

- RESET = Master reset of the AVR, to be connected to a microcontroller supervisory circuit (for example and for information only: MCP809 from Microchip<sup>™</sup>, one possible configuration is given in the next section)

- XTAL1 and XTAL2: input and output to/from the inverting oscillator amplifier

- AREF = analog reference for the A/D internal converter

Finally,  $V_{CC}$  and  $A_{VCC}$  have to be connected to a 3.3V source and GND, to ground.

This gives the following configuration as described in Figure 5-5 on page 10 (AVR only).

**Figure 5-5.** ATmega128L Application Diagram (for Use with e2v EV8AQ160 Quad 8-bit 1.25 Gsps ADC)

Note: Only the connected pins are shown (the unused pins are left open).

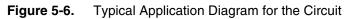

The reset of the ATmega128L AVR can be controlled thanks to a *voltage supervisory circuit* comparable to the MCP809 device from Microchip (for information only). Such a device allows you to keep the micro-controller in reset until the system voltage has reached its final level. It also ensures that the microcontroller will be reset whenever a power drop occurs.

Any voltage supervisory circuit compliant with  $V_{CC} = 3.3V$  and with a reset pulse longer than 50 ns minimum width (active low) would work.

In Figure 5-6 on page 11, the supervisory device from Microchip reset voltage level is set to 3.0V with a pulse of 350 ms.

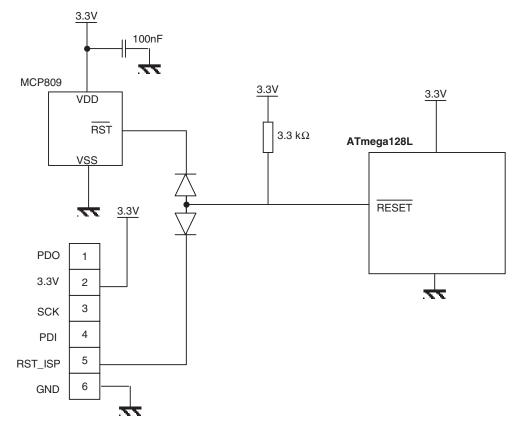

## 5.2 Programming of Atmel ATmega128L AVR

Atmel ATmega128L AVR can be programmed thanks to the AVR ISP (In-System Programmer) tool using AVR Studio<sup>®</sup>, Atmel's Integrated Development Environment (IDE) for code writing and debugging. The programming software can be controlled from both Windows environment and a DOS command-line interface.

For more information on the AVR Studio programming software, please refer to Atmel Website.

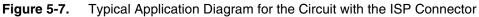

The programming of the AVR requires the use of a 6-pin or 10-pin ISP connector.

In our case, an HE10 6-pin connector is chosen:

- Pin 1 = PDO, AVR Programming Data Out

- Pin 2 = AVR target application card power supply (= 3.3V)

- Pin 3 = SCK, AVR programming clock

- Pin 4 = PDI, AVR Programming Data In

- Pin 5 = RST\_ISP, AVR programming Reset

- Pin 6 = ground

- Note: 1. The ISP card power supply comes from the AVR card (3.3V). There is no need for an additional power supply.

- 2. The mode used to program the AVR is a serial mode.

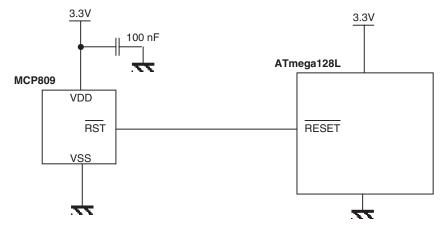

The RST\_ISP signal is used to manage the AVR mode: programming mode or SPI mode.

This signal is sent to the RESET of the AVR so that:

- When RST\_ISP = 0, RESET = 0 and the AVR is in reset (ISP mode), PE0 is used as the Data In for the programming of the AVR, PE1 is the Data Out and PB1 is the programming clock

- When RST\_ISP = 1, RESET = 1 and the AVR is in normal mode, PE0 = RX, PE1 = TX, PB1 = SCLK

The three AVR signals mentioned previously (PE0, PE1 and PB1) ,thus, have two functions controlled by RST\_ISP. Be careful when implementing these signals series resistors on the SCK, PDO and PDI data may be needed to manage possible conflicts, see Section 6.

Similarly, the RESET signal has two possible sources: the signal generated by the microcontroller supervisory device and the RST\_ISP signal from the ISP. In order to manage this signal and in case the microcontroller supervisory device is not with open collector (as for the MCP809 device), two head-to-tail diodes are required, as illustrated in Section 5-7. The line going to the RESET signal of the AVR is then in open-collector and a pull-up resistor (3.3 k $\Omega$ ) to 3.3V is required.

A basic diagram illustrating the interface between the ISP connector and the AVR is depicted in Figure 5-8 on page 13. In this general case, PE1 and PE0 interconnections are left to the user's responsibility. In case of possible conflict on these signals (example PE1 could be driven by both PDO and another signal), it may be necessary to add a 1 k $\Omega$  resistor in series so that any voltage difference will be dissipated in this resistor.

No additional protection is required on the AVR PB1 signal as there is no conflict between SCLK and SCK. It is nevertheless recommended to set the ADC in standby mode or disable the SPI thanks to the CSN bit during programming of the AVR.

Figure 5-8. General Application Diagram for the ISP Connector and the AVR

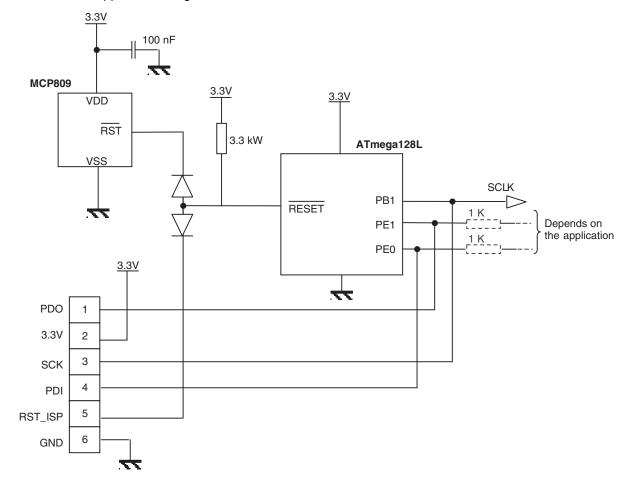

In case the RX and TX signals are to be connected to a transceiver (RS232 connector to a PC for example), in order to multiplex the signals of the AVR (PE0, PE1 and PB1) between the ISP and the RX, TX and SCLK signals, a low voltage buffer/line driver with 3-state outputs device can be used. The 74LVQ241 devices are well-suited for this application (clock driver and bus oriented transmitter or receiver).

The 74LVQ241 device has eight inputs and eight corresponding outputs and two 3-state output enable inputs. These two 3-state output enable inputs can be managed by the RST\_ISP signal:

- When RST\_ISP = 0,  $\overline{OE1}$  = OE2 = 0 and then O<sub>0</sub> to O<sub>3</sub> are low and O<sub>4</sub> to O<sub>7</sub> are in high impedance

- When RST\_ISP = 1,  $\overline{OE1}$  = OE2 = 1 and then O<sub>0</sub> to O<sub>3</sub> are in high impedance and O<sub>4</sub> to O<sub>7</sub> are low

The truth table of the 74LVQ241 device is shown in Table 5-1 on page 14.

| Inputs |                | Outputs                                                                         |

|--------|----------------|---------------------------------------------------------------------------------|

| OE1    | I <sub>n</sub> | (O <sub>0</sub> , O <sub>1</sub> , O <sub>2</sub> , O <sub>3</sub> )            |

| L      | L              | L                                                                               |

| L      | Н              | Н                                                                               |

| н      | Х              | Z                                                                               |

| Inputs |                |                                                                                 |

| OE2    | I <sub>n</sub> | Outputs<br>(O <sub>4</sub> , O <sub>5</sub> , O <sub>6</sub> , O <sub>7</sub> ) |

| L      | Х              | Z                                                                               |

| Н      | L              | L                                                                               |

| Н      | Н              | Н                                                                               |

Table 5-1.74LVQ241Truth Table

Figure 5-9. Typical Application Diagram with the 74LVQ241

- Note: 1. The unused inputs are connected to ground to prevent them from toggling.

- 2.  $\overline{\text{OE1}}$  and OE2 are connected together and to RST\_ISP via a 1 k $\Omega$  resistor.

- SCK, RST-ISP and PDI are connected to I<sub>3</sub>, OE1 and OE2 and I0 respectively via 1 kΩ resistors in order to manage the possible conflicts on the signals in case the connector is used to program several AVRs.

- 4. PE0 is connected to both O<sub>0</sub> and O<sub>4</sub>, which are respectively the inputs corresponding to SCK and RX: PE0 will be either generated by SCK or RX depending on the mode.

- 5. PE1 is connected to both  $I_1$  and  $I_7$ , which are respectively the outputs corresponding to PDO and TX: PE1 will either generate by PDO or TX depending on the mode.

The programming of the AVR itself as well as the connections of the RX and TX signals are not described in this application note as they depend on the final application.

For more information on the AVR, please contact the AVR hotline at avr@atmel.com.

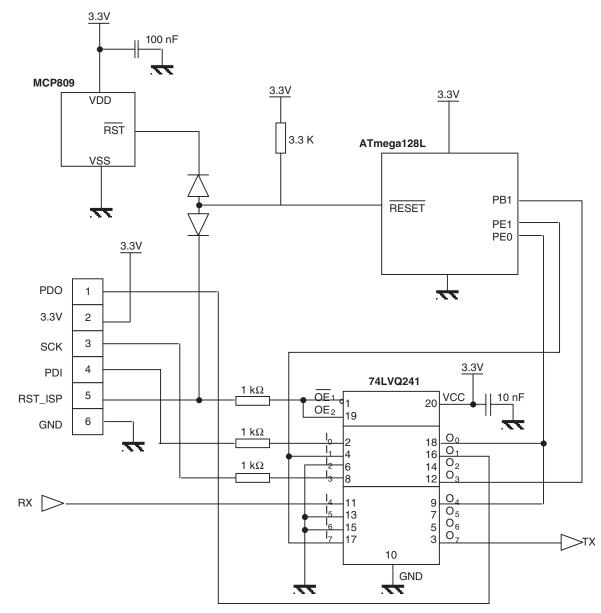

## 6. Grounding and Power Supplies

## 6.1 Ground Plane

One ground plane is necessary for the ADC. It is recommended to separate this ground plane from any other digital ground plane necessary in the system (FPGA, AVR). What is important is that the FPGA and AVR or other digital parts are situated on the board on the same size as the digital part of the ADC (it is important to separate the analog and digital parts).

Note: In the EV8AQ160-EB evaluation board, the ground plane is common to the ADC and the AVR as it is unlikely that the AVR generates perturbations which would cause a degradation of performance of the ADC.

## Figure 6-1. Ground Plane

## 6.2 Power Supply Planes

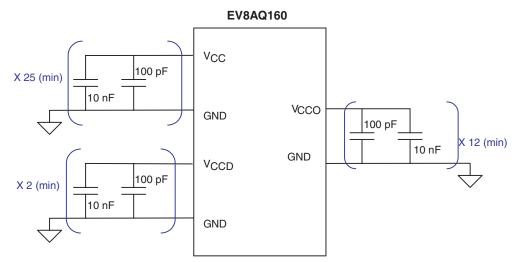

The Quad ADC requires three distinct power supplies:

$V_{CC}$  = 3.3V (for the analog parts and the SPI pads)

$V_{CCD} = 1.8V$  (for the digital parts)

$V_{CCO} = 1.8V$  (for the output buffers)

It is recommended to decouple all power supplies to ground as close as possible to the device balls with 100 pF in parallel to 10 nF capacitors. The minimum number of decoupling pairs of capacitors can be calculated as the minimum number of groups of neighboring pins.

25 pairs of 100 pF in parallel to 10 nF capacitors are required for the decoupling of  $V_{CC}$ . 12 pairs for the  $V_{CCO}$  is the minimum required and finally, one or two pairs are necessary for  $V_{CCD}$ .

Figure 6-2. Power Supplies Decoupling Scheme

Each power supply should be bypassed as close as possible to its source or access by 100 nF in parallel to 1  $\mu$ F capacitors.

## 6.3 Board Layout Recommendations

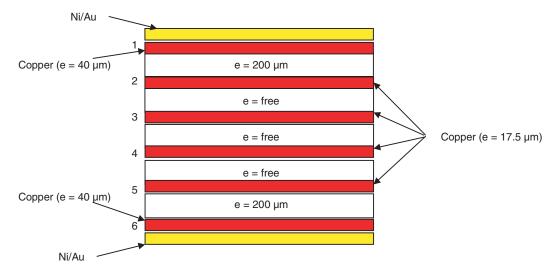

### 6.3.1 PCB Stack Up

The recommended board stack up is described in Figure 6-3 on page 18.

It applies to ISOLA410 PCB board material.

Figure 6-3. Board Recommended Stack Up Using ISOLA 410 Board Material

## 6.3.2 Clock, Analog Input And Output Data Signals

It is recommended to route the clock, analog input signals and output data signals as differential signals.

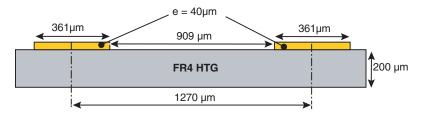

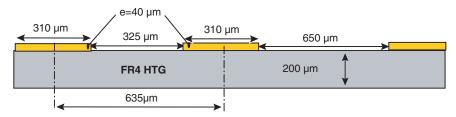

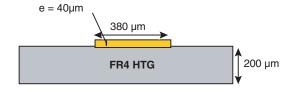

In the case of the use of a PCB with dielectric material such as FR4 HTG (ISOLA IS410 with 42% resin content and  $\varepsilon_t = 4$ ), the recommended board layout for the differential signals (clock and analog inputs) is described in Figure 6-4 and Figure 6-5 on page 19. This recommended layout only applies if the board stack up described in section Section 6.3.1 is satisfied.

Note: In the case of the digital output signals, the recommended differential routing is provided in Figure 6-5 on page 19.

Figure 6-4 shows the standard routing with 1.27 mm pitch between signals of the same differential pair (clock and analog inputs only).

Figure 6-5 on page 19 shows another possible routing for differential signals (clock analog inputs and digital outputs), preferred in case of high board size constraints.

Both configurations satisfy the impedance matching required for differential signals.

Figure 6-4. Differential Board Routing for The Clock and Analog Input Signals on FR4 HTG (IS410)

# **Figure 6-5.** Differential Board Routing for the Clock, Analog Input and Digital Output Signals on FR4 HTG (IS410)

In the case of single-ended signals, the board layout should be as illustrated in Figure 6-6.

**Figure 6-6.** Single-ended Routing on FR4 HTG (IS410)

# e2v

## How to reach us

Home page: www.e2v.com

#### Sales Office:

# Northern Europe

**e2v Itd** 106 Waterhouse Lane Chelmsford Essex CM1 2QU England Tel: +44 (0)1245 493493 Fax:: +44 (0)1245 492492 E-Mail: enquiries@e2v.com

#### Southern Europe

**e2v sas** 16 Burospace F-91572 Bièvres Cedex France Tel: +33 (0) 16019 5500 Fax: +33 (0) 16019 5529 E-Mail: enquiries-fr@e2v.com

#### Germany and Austria

**e2v gmbh** Industriestraße 29 82194 Gröbenzell Germany Tel: +49 (0) 8142 41057-0 Fax:: +49 (0) 8142 284547 E-Mail: enquiries-de@e2v.com Americas e2v inc. 4 Westchester Plaza Elmsford NY 10523-1482 USA Tel: +1 (914) 592 6050 or 1-800-342-5338, Fax: +1 (914) 592-5148 E-Mail: enquiries-na@e2v.com

#### Asia Pacific

e2v Bank of China Tower 30th floor office 7 1 Garden Rd Central Hong Kong Tel: +852 2251 8227/8/9 Fax:: +852 2251 8238 E-Mail: enquiries-hk@e2v.com

#### Product Contact:

e2v Avenue de Rochepleine BP 123 - 38521 Saint-Egrève Cedex France Tel: +33 (0)4 76 58 30 00 Hotline: hotline-bdc@e2v.com